DS160PT801 PCIe® 4.0, 16Gbps, 8-Lane (16-Channel) Retimer

1 Features

• 8-Lane (16-Channel) Protocol-Aware PCI-Express

Retimer supporting 16.0, 8.0, 5.0, and 2.5 GT/s

Interfaces

• Inter-Chip Communication (ICC) Enable Dual Chip

Link Width Scaling to form 16-Lane Gen-4 Retimer

• Supports Common Clock, Separate Reference

Clock with no SSC, and Separate Reference Clock

with SSC

• Supports 2x4 and 4x2 Bifurcation

• Adaptive Receive CTLE and DFE Supporting

Maximum PCIe Gen-4 Channel Loss

• Supports Equalization Training

• Low-Latency Architecture

• On-Chip Eye Opening Monitor (EOM) and PCIe

Receive Margining Capability

• Small 8.5-mm x 13.4-mm BGA Package

• Flow-Through Pinout Enables Signal Breakout in

Two Signal Layers

• Compatible with Standard 1.0-mm BGA PCB

Manufacturing

• Dual Power Supply: 1.1 V and 1.8 V

• I2C Configuration (up to 1 MHz) via External

EEPROM or I2C Master

• Industrial Temperature Range: -40 °C to 85 °C

2 Applications

• Rack server

• Microserver & tower server

• High performance computing

• Hardware accelerator

3 Description

The DS160PT801 is a high-performance eight-lane

(16-channel) PCI-Express protocol-aware retimer

supporting all standard PCIe data rates up to 16 GT/s.

It is used to extend the reach and robustness of high-

speed PCIe serial links, from chip-to-chip

motherboard links to more complex multi-connector

system topologies.

The DS160PT801 supports both common-clock and

independent reference clock architectures, with and

without spread-spectrum clocking. This allows for

maximum flexibility in defining the system clock

architecture.

The eight lanes in the DS160PT801 can be bifurcated

into two x4 or four x2 links to support different system

topologies.

A compact yet easy-to-manufacture BGA package

provides excellent thermal performance while

enabling optimal placement in space-constrained

applications like 1RU riser cards. This feature reduces

overall solution size, PCB routing complexity, and

BOM cost.

Diagnostic capabilities include in-band receiver

margining, out-of-band non-destructive horizontal/

vertical eye margin monitor, receiver loopback,

encoding error detection, and on die temperature

sensor. These features help gauge link margin and

can be used to monitor system health over time.

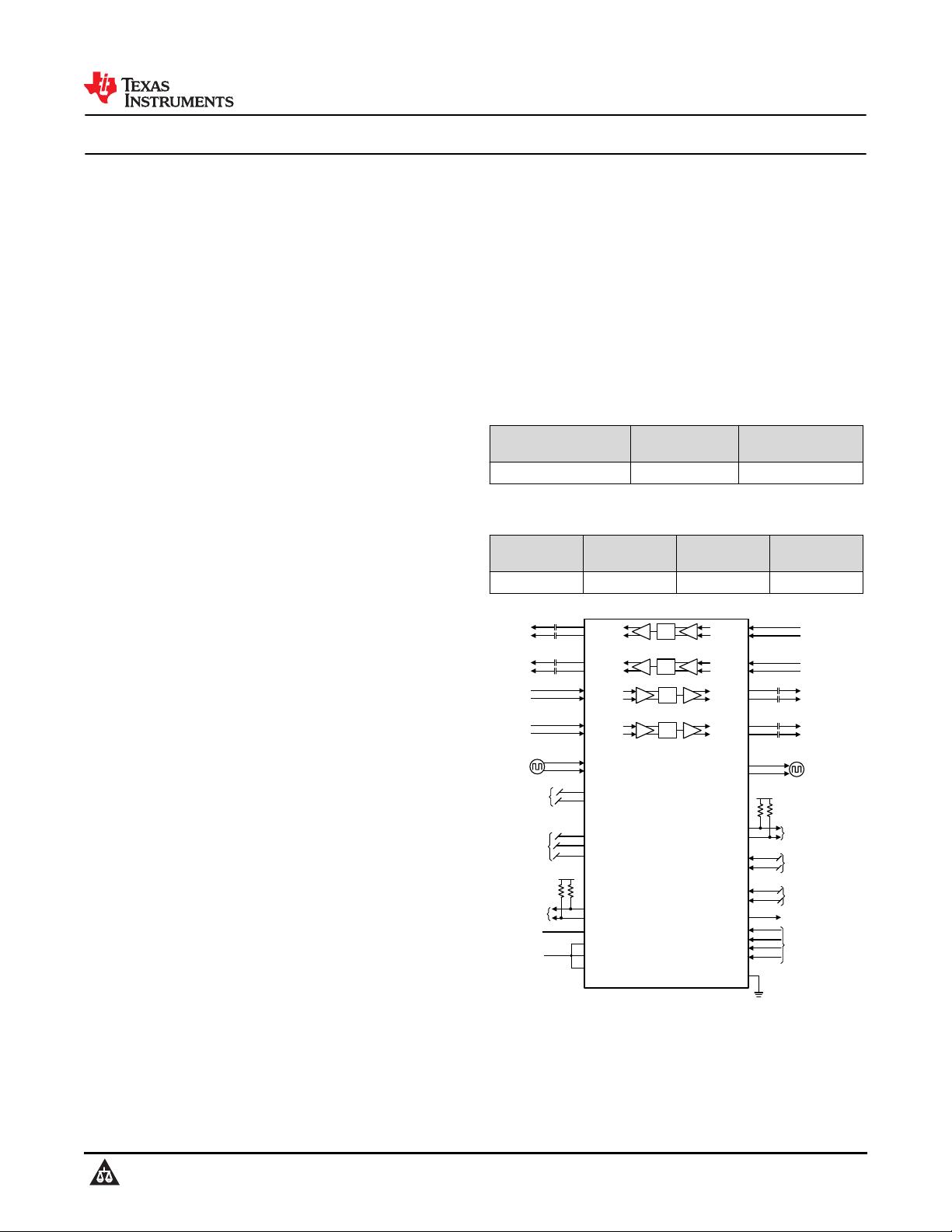

Device Information

(1)

ORDERABLE PART

NUMBER

PACKAGE BODY SIZE (NOM)

PDS160PT801C0ACBT 332-pin fcBGA 8.5 mm x 13.4 mm

Device Comparison Table

PART

NUMBER

LINK WIDTH PCIe GEN DEVICE TYPE

DS160PT801 x8 4, 3, 2, 1 Retimer

PWR_2B

SMBDAT

SMBCLK

GND

MODE

Address straps

(pull-up, pull-

down, or float)

To system SMBus

1.8 to 3.3V

REFCLK+

B_PERp0

B_PETp0

B_PERn0

B_PETn0

CDR

B_PERp7

B_PETp7

B_PERn7

B_PETn7

CDR

.

.

.

.

.

.

CDR

A_PETp0

A_PERp0

A_PETn0

A_PERn0

CDR

A_PETp7

A_PERp7

A_PETn7

A_PERn7

.

.

.

.

.

.

REFCLK-

SMB_ADDR_0

SMB_ADDR_1

Multi-level strap

(pull-up, pull-

down, or float)

JTAG_TDO

JTAG_TDI

JTAG_TCK

JTAG_TMS

JTAG_TRST#

From system

JTAG up to 3.3V

tolerance

PERST#

CLKREQ#

RX_DET_BYP

PWR_2A

PWR_1

Strap or system-

controlled up to

3.3V tolerance

VDD1.8V

VDD1.1V

EE_CLK

EE_DAT

To optional

EEPROM

1.8 to 3.3V

WIDTH

PRT0_RST#

PRT1_RST#

Strap or system-

controlled up to

1.8V tolerance

100 MHz

100 MHz

REFCLK_OUT+

REFCLK_OUT-

To system JTAG up

to 1.8V tolerance

PWR_2C

Simplified Schematic

www.ti.com

DS160PT801

SNLS592 – DECEMBER 2020

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

1

Product Folder Links: DS160PT801

DS160PT801

SNLS592 – DECEMBER 2020

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. ADVANCE INFORMATION for preproduction products; subject to change

without notice.