利用Logisim与Verilog设计与验证组合逻辑电路

需积分: 0 115 浏览量

更新于2024-08-05

收藏 612KB PDF 举报

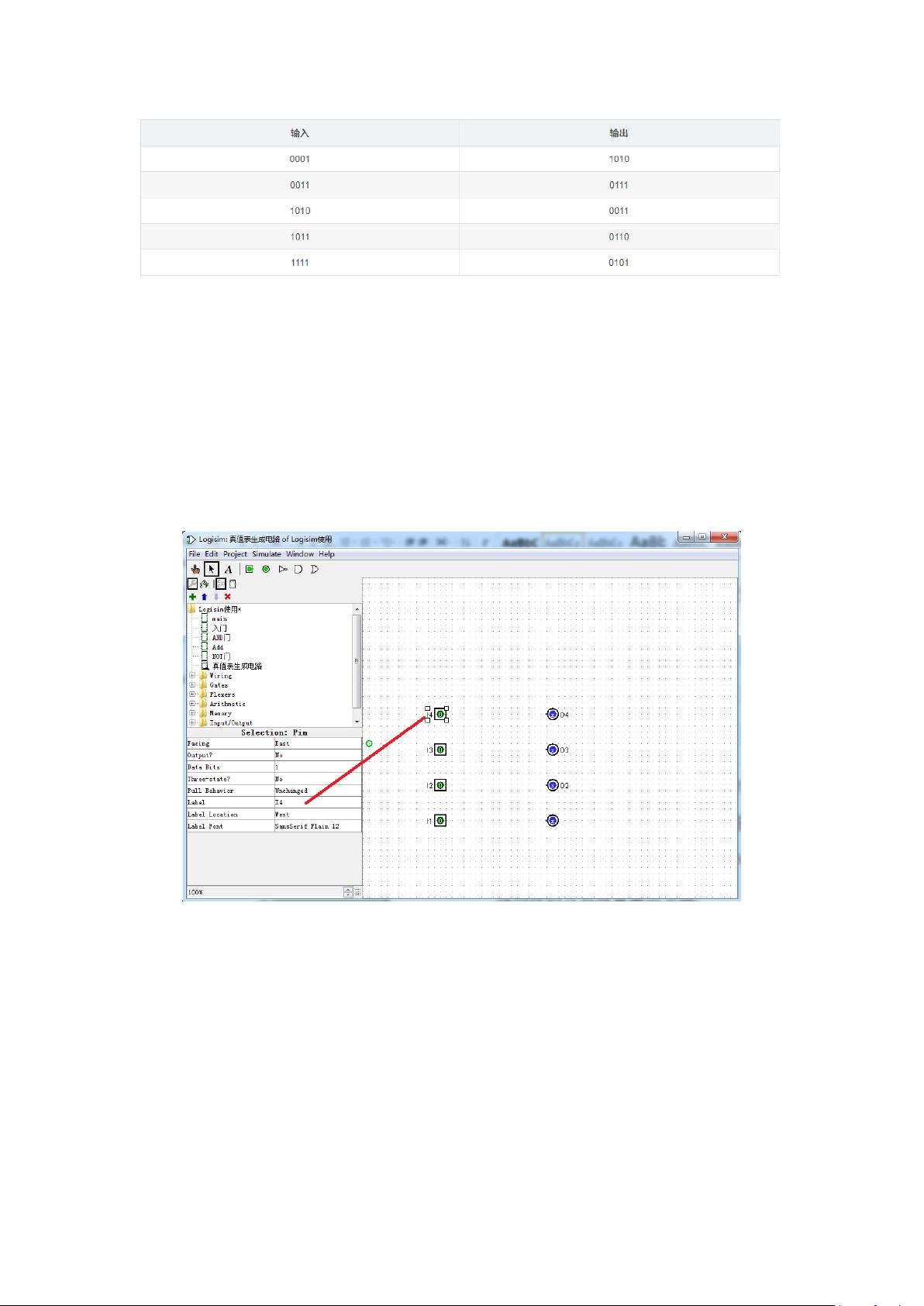

实验02_简单组合逻辑电路1深入介绍了数字电路设计的一般流程和关键步骤,主要围绕Verilog硬件描述语言、Vivado综合工具以及FPGA实验平台展开。实验旨在帮助学生掌握Logisim这款教学工具,它是电路设计的入门级工具,用于电路原理和功能的仿真,但不能替代真正的电路实现。

1. **电路设计流程**:

实验首先从电路描述开始,通过Verilog这种硬件描述语言来编写电路的逻辑功能。Verilog是一种高级的硬件描述语言,允许开发者以软件开发的方式描述电子系统的逻辑结构,这与传统的编程语言类似,但目标是生成实际的硬件实现。

2. **电路实现与仿真**:

使用Vivado作为综合工具,它能够将Verilog代码转化为可编程逻辑器件(FPGA)可以直接执行的逻辑网络。Vivado提供了设计、仿真和部署的完整流程,对于复杂电路设计来说,这是不可或缺的一步。

3. **FPGA实验平台**:

FPGA实验平台是将设计的电路在硬件上实际运行的载体,它允许学生将理论知识付诸实践,观察和验证电路的实际行为。

4. **电路仿真与异常验证**:

通过Logisim进行电路仿真,可以预先检查设计的正确性,发现并修复可能存在的问题。此外,实验还涉及功能验证,确保电路按照预期工作。

5. **代码修改与设计迭代**:

实验过程中,学生需要不断修改和优化代码,以实现更高效、更精确的电路设计。这包括理解并掌握Verilog语法,以及如何根据需求调整电路设计。

6. **Logisim的应用**:

Logisim在实验中扮演着重要的角色,它是教学辅助工具,有助于初学者理解逻辑门和布尔代数。尽管功能有限,但它提供了一个直观的环境,帮助学生从原理学习到实际操作。

7. **实验环境**:

学生需要具备基本的PC配置,如Windows或Linux操作系统,以及Java运行环境,同时Logisim仿真工具和相关教程资源可在指定网站获取。

8. **实验步骤**:

实验分为多个步骤,包括使用真值表自动生成电路,利用Logisim设计电路图,根据逻辑表达式绘制电路,最后进行功能验证和代码优化。每个步骤都是从抽象的逻辑概念到具体实现的必要环节。

通过这个实验,学生不仅能够提升逻辑电路设计的技能,还能够理解和掌握硬件描述语言的基础知识,为后续更复杂的电路设计和硬件实现打下坚实基础。

2022-08-08 上传

2011-07-21 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-08 上传

2024-07-16 上传

2022-08-03 上传

郑瑜伊

- 粉丝: 23

- 资源: 317

最新资源

- Haskell编写的C-Minus编译器针对TM架构实现

- 水电模拟工具HydroElectric开发使用Matlab

- Vue与antd结合的后台管理系统分模块打包技术解析

- 微信小游戏开发新框架:SFramework_LayaAir

- AFO算法与GA/PSO在多式联运路径优化中的应用研究

- MapleLeaflet:Ruby中构建Leaflet.js地图的简易工具

- FontForge安装包下载指南

- 个人博客系统开发:设计、安全与管理功能解析

- SmartWiki-AmazeUI风格:自定义Markdown Wiki系统

- USB虚拟串口驱动助力刻字机高效运行

- 加拿大早期种子投资通用条款清单详解

- SSM与Layui结合的汽车租赁系统

- 探索混沌与精英引导结合的鲸鱼优化算法

- Scala教程详解:代码实例与实践操作指南

- Rails 4.0+ 资产管道集成 Handlebars.js 实例解析

- Python实现Spark计算矩阵向量的余弦相似度