Verilog设计深入:六十进制计数器与七段码译码器

需积分: 7 79 浏览量

更新于2024-07-17

收藏 1.76MB PPTX 举报

本资源是关于Verilog设计深入的PPT教程,主要涵盖了对Verilog设计的深入理解和应用,特别是过程语句和赋值语句的使用,通过实例讲解了六十进制BCD码计数器显示电路以及七段码译码器的设计。

在Verilog设计中,过程语句是实现逻辑控制的关键部分。本章首先回顾了两类赋值语句,即连续赋值语句和过程赋值语句。连续赋值语句(如`=`)用于时不变的逻辑关系,而过程赋值语句(如`always`块内的`<=`)则用于时序逻辑的描述。这两类赋值语句在程序设计中有各自的应用场景,理解它们的差异对于编写高效且准确的Verilog代码至关重要。

课程中详细讲解了一个设计实例——六十进制BCD码计数器显示电路。这个设计涉及到非完整条件的`if-else`语句,它允许在满足特定条件时执行不同的逻辑路径。通过这样的设计,可以实现计数器在六十进制模式下循环计数,并将BCD码转换为适合七段显示器的输出。

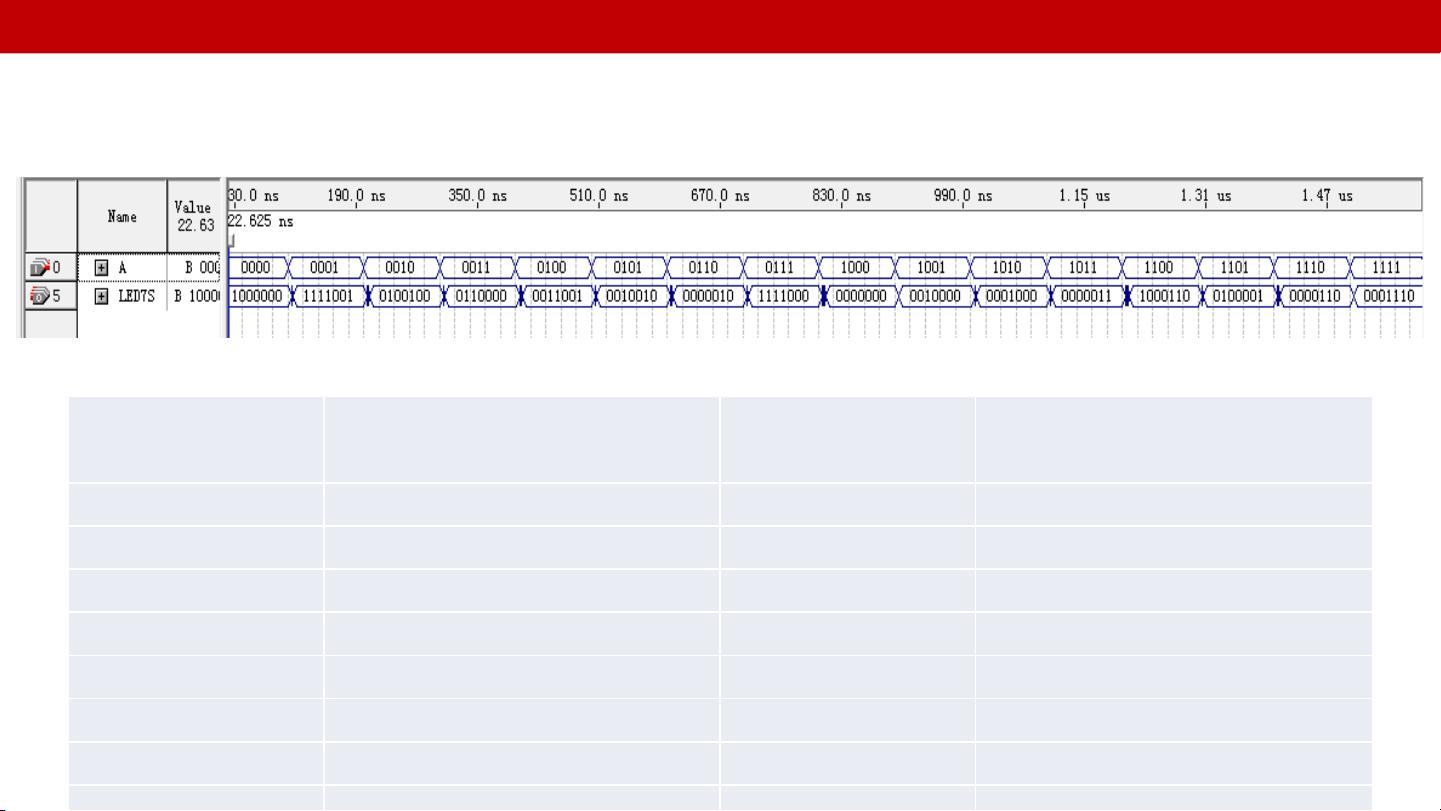

接着,课程介绍了七段码译码器的设计,这是一种将四位二进制输入转换为七段显示输出的逻辑电路。这里使用了`case`语句,它是一种结构化的多路选择语句,可以根据输入的BCD码值选择对应的七段码输出。在Verilog代码中,`case`语句的使用使得代码更易于阅读和维护。课程分别展示了共阴极和共阳极七段码译码器的工作原理和真值表,并给出了具体的Verilog实现代码。

在七段码译码器的Verilog设计中,`always`块被用来描述时序逻辑。根据输入`A`的值,内部寄存器`LED7S`的值被设置为对应的七段码。`default`语句用于处理未定义的输入值,确保在未知或非法输入时有默认的显示状态。

这个PPT教程深入探讨了Verilog设计中的关键概念和技术,包括过程语句的使用、条件逻辑控制以及基于`case`的多路选择,这些都是数字系统设计中的基础元素。通过学习这些内容,开发者能够更好地理解和构建复杂的电子电路。

2021-09-23 上传

2021-10-07 上传

2021-10-05 上传

2022-10-16 上传

2021-09-23 上传

2021-10-08 上传

2021-09-21 上传

2021-10-03 上传

2024-05-22 上传

Dupreeh_

- 粉丝: 0

- 资源: 1

最新资源

- vb语言程序设计教程.zip

- sjasmplus:SJAsmPlus

- A06:作业6

- GnomeNibus-开源

- message-franking-tester:实施不同的邮件盖章方案和性能分析测试仪

- 机器学习python标记工具-Labelimg2024

- React-Portfolio:我的一小部分作品,用React重写

- MM32SPIN0x(s) 库函数和例程.rar

- goApi

- cuetools-开源

- Veni-Vidi-Voravi

- website:Terre Tropicale公共网站

- Main:基于struts2库存管理系统Android端

- Another-React-Lib:只是另一个充满可重用组件的React库

- 华为简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 原型