"系统Verilog实验手册"

需积分: 16 140 浏览量

更新于2024-01-04

收藏 24.1MB PDF 举报

本实验手册为Synopsys公司的system Verilog LAB实验手册,旨在通过一系列实验帮助学习者更好地理解和掌握system Verilog编程语言以及测试平台的使用方法。手册中提供了详细的实验指导和实验步骤,使学习者能够逐步掌握system Verilog的语法和应用。

实验手册的内容主要包括以下几个方面:

1. 实验准备:介绍了实验所需的软件和硬件环境,以及相关的安装和配置。

2. 实验一:介绍了system Verilog的基本语法和数据类型,包括变量定义、运算符、控制语句等。通过实例演示了如何使用system Verilog进行简单的算术运算和逻辑判断。

3. 实验二:深入探讨了system Verilog的模块化编程和层次结构,包括模块定义、端口连接、实例化等。通过实例演示了如何创建和使用多个模块,以及模块之间的通信。

4. 实验三:介绍了system Verilog中的任务和函数,包括任务和函数的定义、参数传递、返回值等。通过实例演示了如何使用任务和函数实现复杂的功能。

5. 实验四:重点讲解了system Verilog中的并发编程和时序控制,包括并发程序、时钟信号、阻塞和非阻塞赋值等。通过实例演示了如何设计和实现时序控制器和状态机。

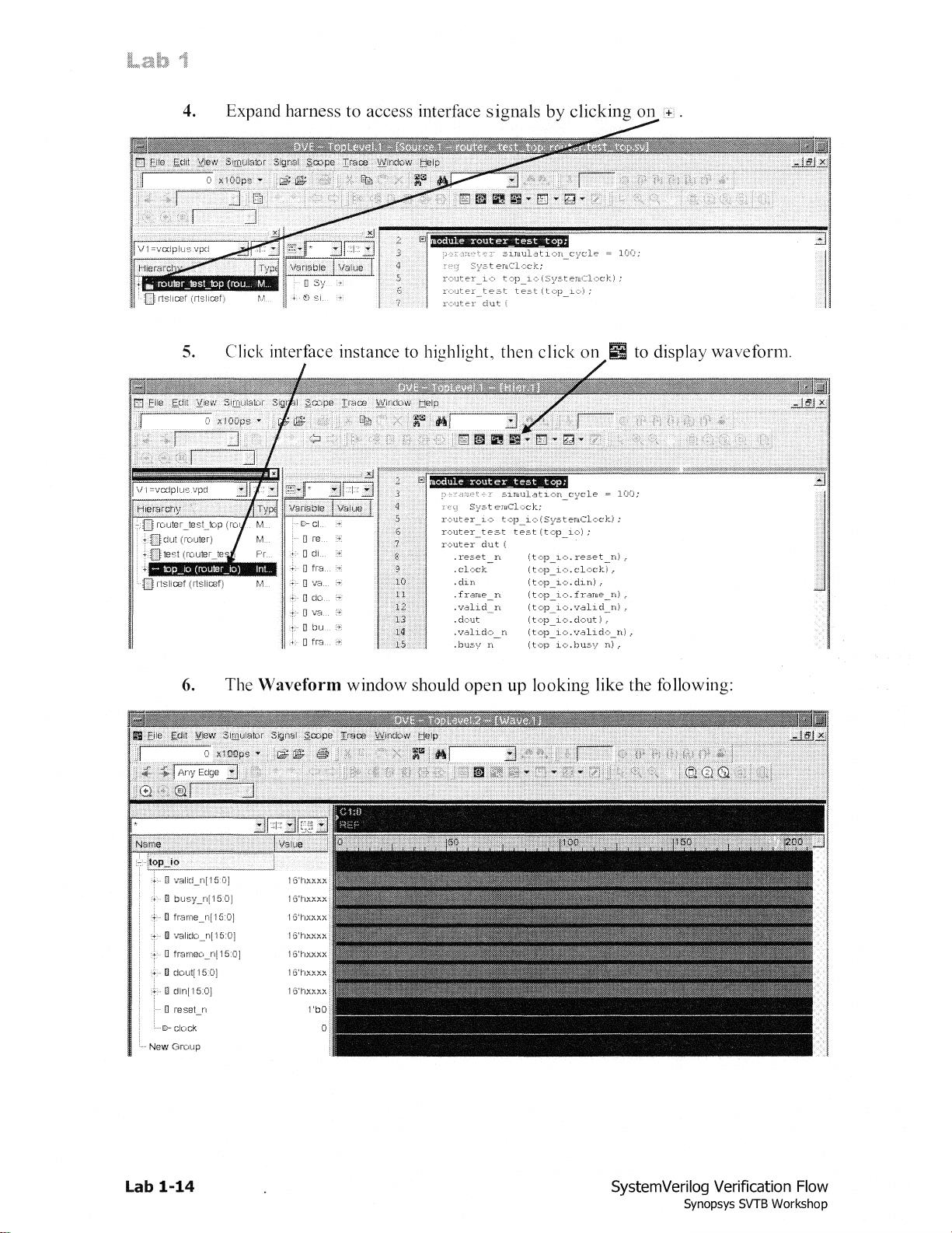

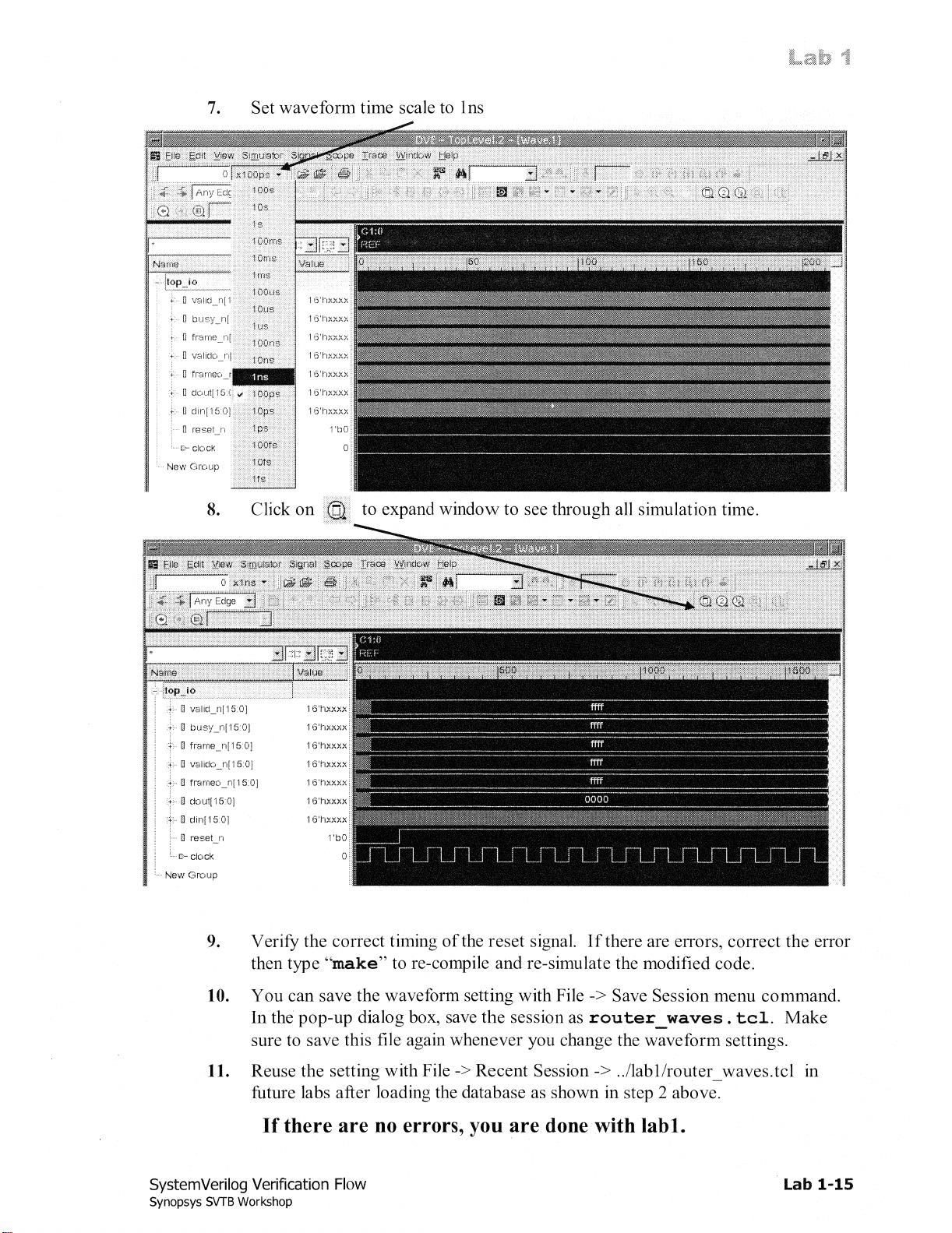

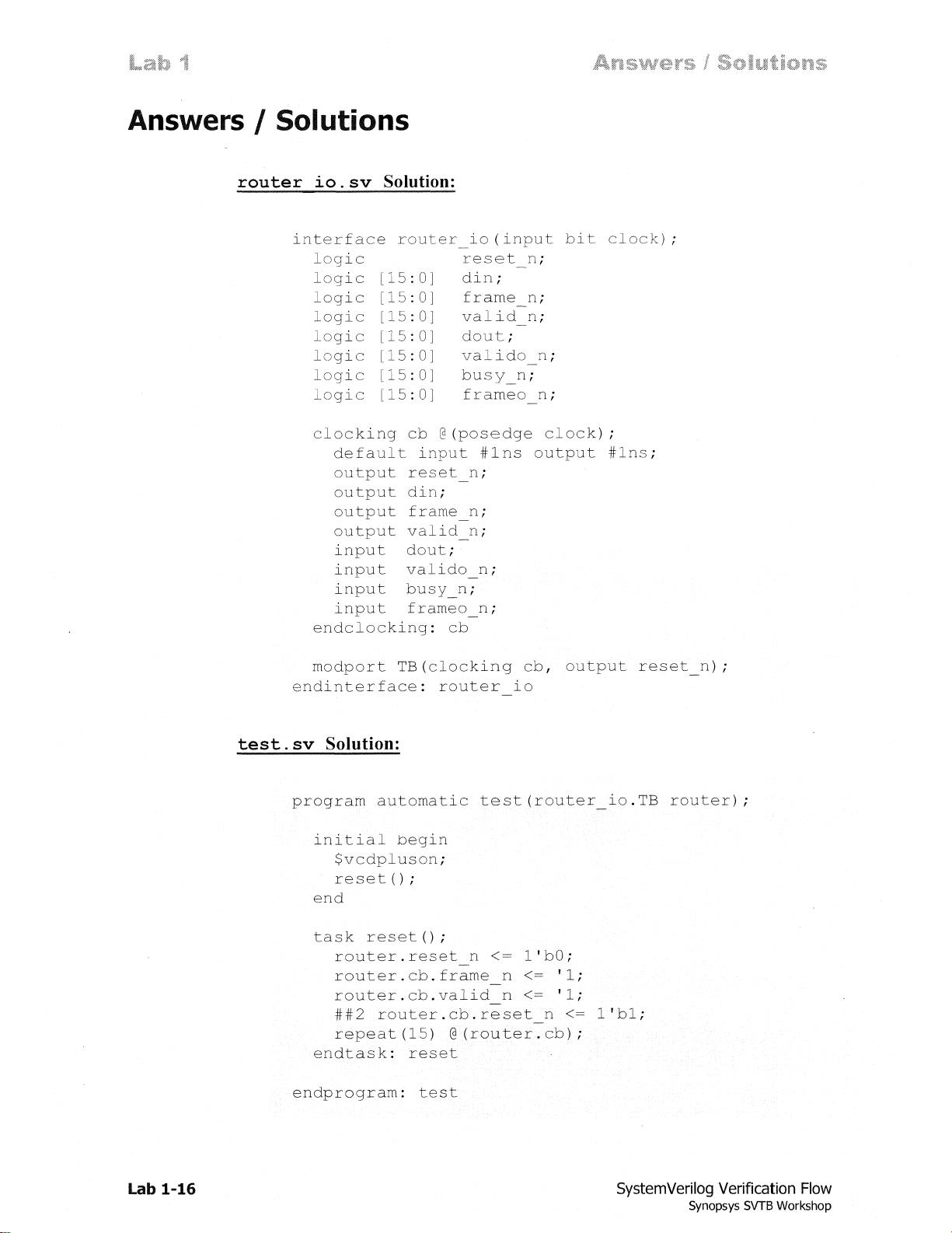

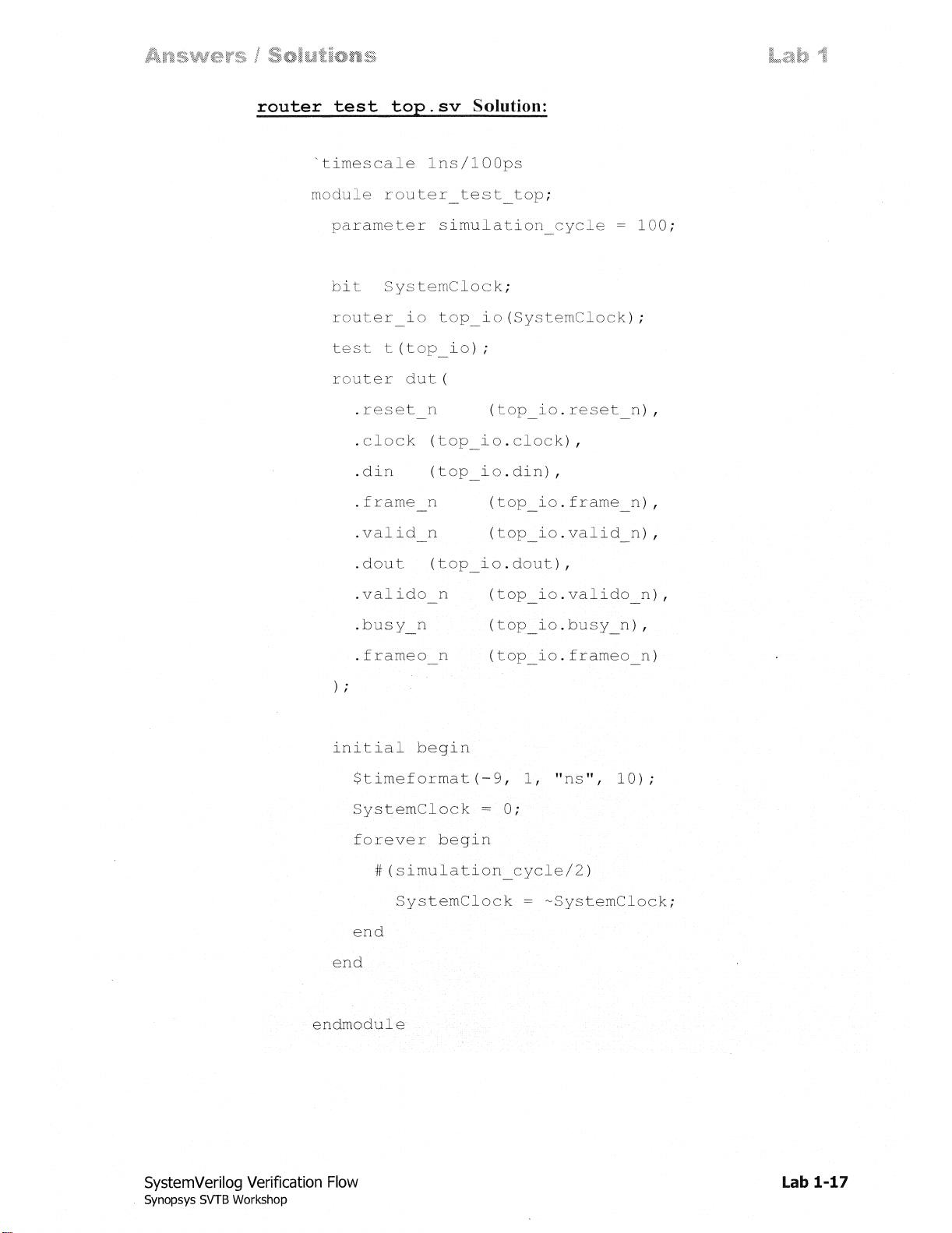

6. 实验五:介绍了system Verilog的测试平台和测试构建,包括testbench的编写、信号生成和波形分析等。通过实例演示了如何编写和执行测试用例,以及如何分析波形和结果。

7. 实验六:探讨了system Verilog中的断言和覆盖率,包括断言的定义和使用、覆盖率的评估和优化等。通过实例演示了如何编写断言和覆盖率代码,以及如何进行验证和优化。

实验手册不仅提供了详细的实验内容和实验步骤,还附带了相关的实例代码和实验数据,方便学习者进行实验和验证。

总的来说,本实验手册通过一系列实验帮助学习者掌握system Verilog编程语言和测试平台的使用方法。手册内容详尽,实例丰富,适合系统Verilog初学者和从事系统级设计和验证工作的工程师使用。通过使用本实验手册,学习者可以更好地理解和应用system Verilog编程语言,提高系统级设计和验证的效率和质量。

157 浏览量

124 浏览量

129 浏览量

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

1151 浏览量

星星之火可以燎原

- 粉丝: 4

- 资源: 1

最新资源

- detectBrowserVisibility:检测浏览器可见性状态变化

- stomp-websocket-server:使用Spring的STOMP实现Websocket服务器

- python代码自动办公 Excel_案例_用Excel画画项目源码有详细注解,适合新手一看就懂.rar

- jQuery带备忘录功能的日期选择器特效代码

- NAS-DIP-pytorch:[ECCV 2020] NAS-DIP

- kj6682-library:我的图书馆

- Archive-1844_C++_

- 互联网站点:存储库,可扩展性或永久性

- breakout-rooms:分组讨论室附加到Jitsi Meet和Jitsi Videobridge项目中

- PHP实例开发源码-易优实验报告管理系统 PHP源码 v1.0.zip

- bikeshop:网络开发课程项目

- python代码自动办公 用Python在Excel中查找并替换数据 项目源码有详细注解,适合新手一看就懂.rar

- KonradLinkowski:我的GitHub操作配置文件README :)

- WEB1:某种html内容

- Node-Chat:建立在Node.js,Socket.io和WebRTC上的类似omegle的应用程序

- Leveon Bell HD Wallpapers Game Theme-crx插件