Xilinx FPGA配置流程详解与要点

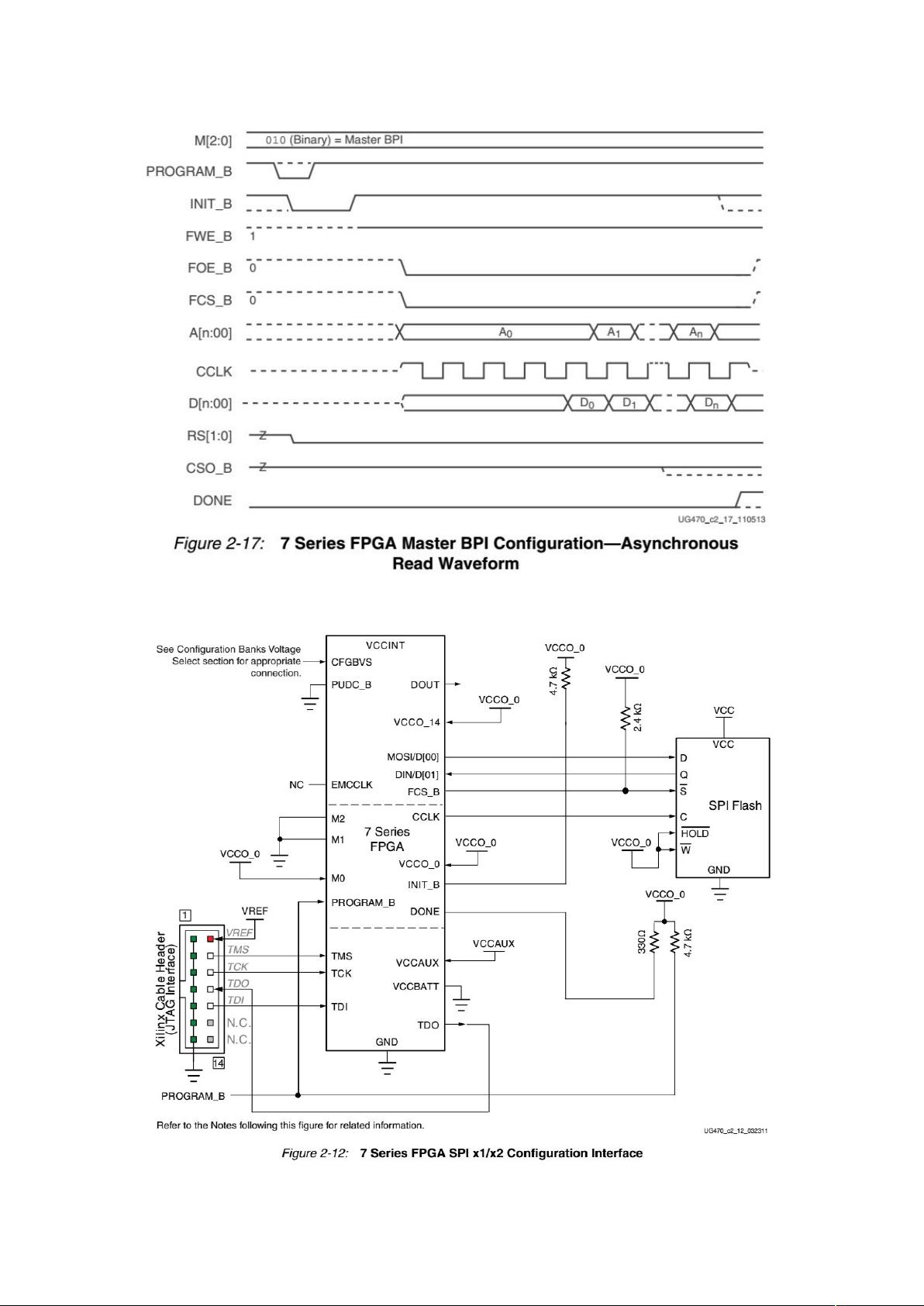

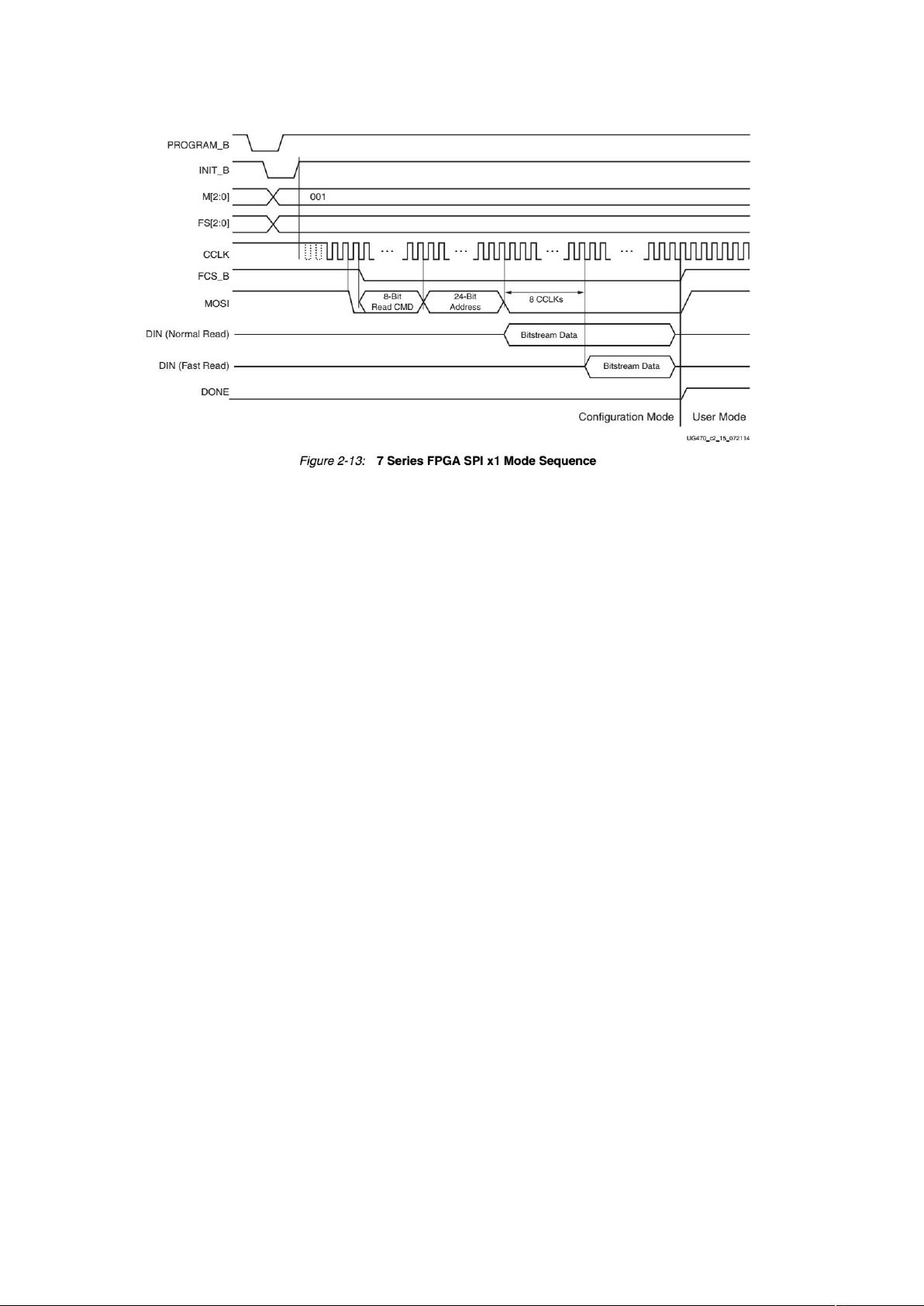

本文档详细总结了Xilinx FPGA的硬件设计流程,特别是针对Xilinx 7系列FPGA的配置过程。FPGA配置分为三个关键阶段:设置、加载和启动。

首先,配置过程在FPGA复位结束后开始。可以通过电源上电或PROG_B引脚的低脉冲触发复位。在复位期间,配置存储器内容会被清除,所有非配置专用接口处于高阻态,而INIT_B引脚则用于初始化阶段。若外部强制使INIT_B低,FPGA将保持初始化状态,直到收到正确的模式选择和变量选择信号。

在初始化完成后,FPGA开始同步模式。同步头,即特定的同步字,用来标识配置数据的开始,确保数据的正确采样。FPGA在配置时钟上升沿采样配置数据,对数据进行校验,确保数据一致性。如果遇到不一致的器件ID,FPGA会停止配置,并可能显示错误信息。

接着是数据载入阶段,FPGA执行CRC(循环冗余校验)来验证每帧数据的完整性,如果有误,配置过程会中断。在数据载入成功后,FPGA会按照预设的启动序列进行操作,例如释放DONE引脚,激活I/O以及启动写使能,这些步骤可以通过BitGen参数进行自定义设置,以适应不同的应用需求。

Xilinx 7系列FPGA具有灵活的配置模式,但无论哪种模式,核心流程都围绕着这三个步骤进行。对于硬件设计者来说,理解并掌握这个流程至关重要,因为它直接影响到FPGA的正确配置和性能表现。这份总结提供了宝贵的实践经验和参考,对深入学习和进行高效硬件设计具有很高的价值。

2020-04-17 上传

2022-04-22 上传

2021-09-25 上传

2010-06-08 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

windydfl

- 粉丝: 5

- 资源: 8

最新资源

- 减去图像均值matlab代码-Cropmeasure:测量作物绿色度的简单代码,不太可能对任何人有用

- Hewi_ios:它是在项目实践期间开发的ios小部件应用程序。

- IT_Logger:ReactRedux应用程序可跟踪IT部门的任务和问题

- eks-microservice:AWS EKS Microservice-易于设置

- ANNOgesic-1.0.20-py3-none-any.whl.zip

- idk

- 使用MFC打印和打印预览OpenGL

- computationalIntelligence:计算智能讲座练习@ ZHAW 2015

- weather_crawl:抓取工具收集韩国的天气信息

- project-fusion:Boilerplate Web入门工具包,既实用又灵活。 旨在使开发人员快速启动并运行并保持敏捷。 高度自动化和开箱即用的支持ES6,JSPM,Gulp,Babel,Karma和Mocha。 能够使用SC5样式指南和KSS语法自动生成样式指南。 使用Backstop jSCSS回归测试。 Nunjucks模板。 基于git提交历史记录和注释的自动发布(颠簸重新推荐,changelog文件生成和github自动发布)。 使用ESDoc自动生成Javascript文档。 模块化设

- Web_HC_ZL_Javascript_Slider:网页赫彩中坜JS应用轮播套件

- ALGOpractice

- 创建屏幕-Android UI布局和控件

- 旅游公司网站模版

- DMOJJava解决方案

- java长途客车网上售票系统分析与设计(含毕业论文和sql文件)