数字逻辑期末考试题集精选:必做组合逻辑与触发器题目

需积分: 12 126 浏览量

更新于2024-07-20

收藏 2.66MB DOC 举报

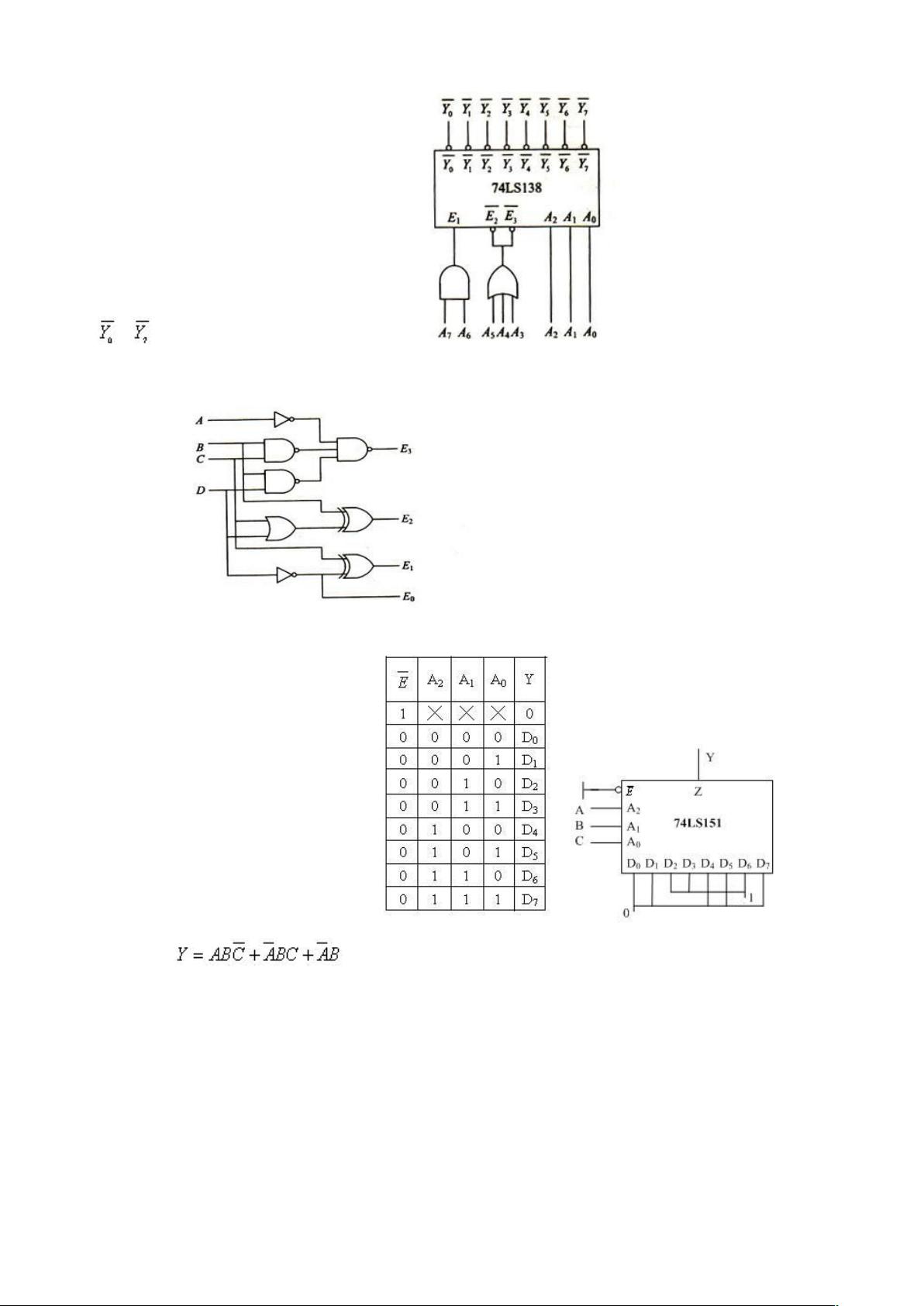

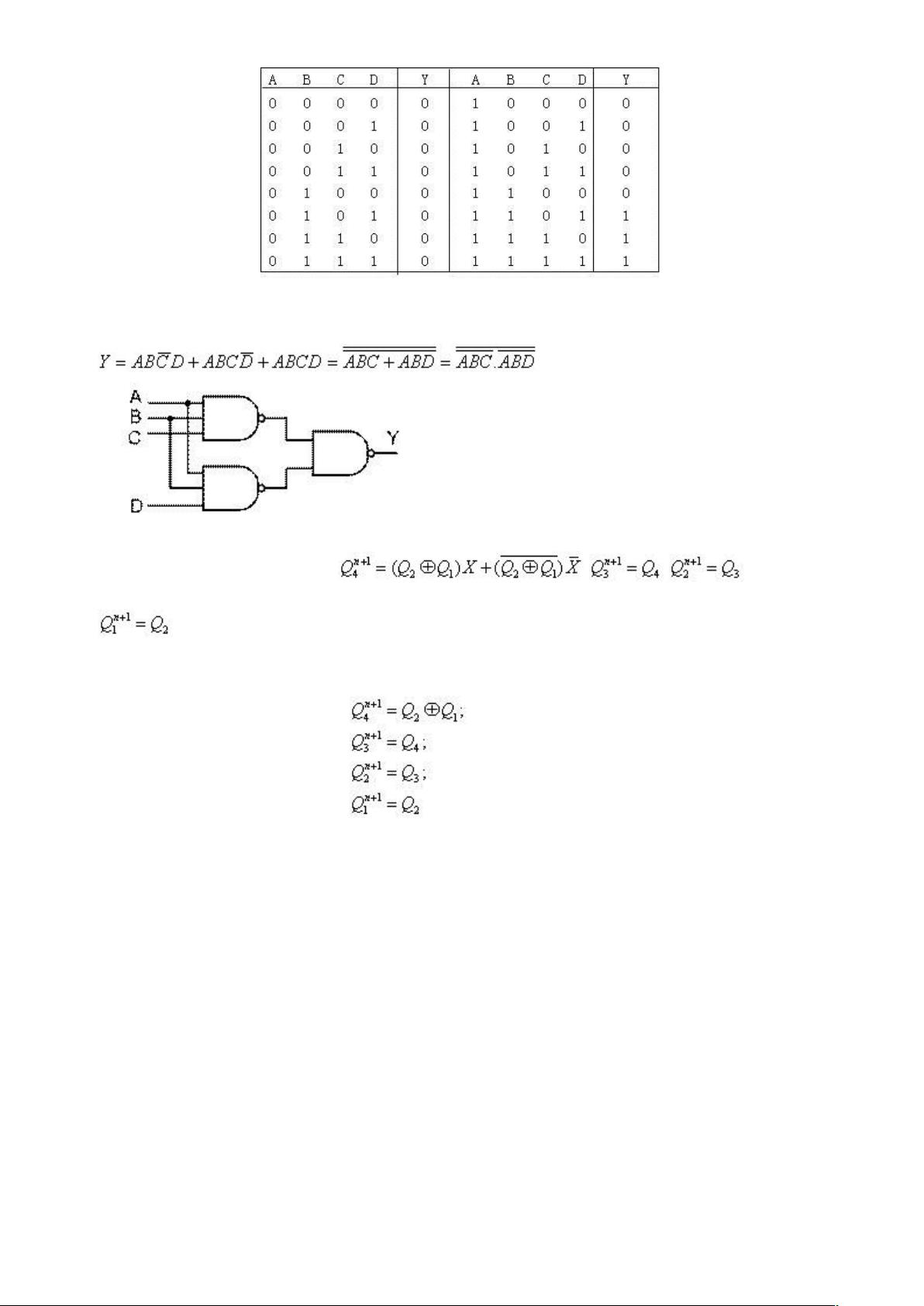

本资源是一份针对12级网络工程专业的数字逻辑期末考试题库,包含30道选择题,主要考察学生对数字逻辑基础知识的理解和应用。题目的范围广泛,涉及了二进制补码表示、组合逻辑电路设计、触发器功能、编码器和译码器的区别、优先级编码器的使用、555定时器的内部结构、计数器的构成、不同类型的触发器特性、数字转换、逻辑运算、最大数比较、门电路的功能、以及逻辑电路的分类等核心知识点。

1. 学生需要掌握二进制小数的补码表示,例如第1题提到的-0.0110的补码形式,正确答案是B选项1.1001,这涉及了补码的概念和计算方法。

2. 第2题涉及的是实现组合逻辑函数的电路选择,其中译码器常用于实现多个输入对应多个输出的逻辑函数,因此B选项正确。

3. D触发器作为T′触发器时,输入控制端D应接成非门的形式,对应的标准答案是B,这考察了时序逻辑电路的基本原理。

4. 在数字逻辑设计中,全加器是一种基础组件,用于处理三位数的加法,因此全加器需要三个输入变量,即A、B和Cin,选项A(3个)是正确的。

5. 边沿数据锁定触发器是一种性能增强的主从触发器,C选项正确,这要求学生理解不同触发器类型的特点。

6. 题目中给出了逻辑函数的真值表,要求找出与其等价的表达式,通过分析给出的选项,D选项可能是正确答案,但具体判断需要完整的真值表来确定。

7. 对于74LS147这个二-十进制优先级编码器,当输入为111111111时,输出应该是最低有效位的编码,即1110,对应C选项。

8. 555电路是一个经典的模拟集成电路,包含2个比较器、1个RS触发器、1个驱动器和1个放电晶体管,选项C(2,1)符合题意。

9. 十进制计数器至少需要4个触发器才能实现至少0到9的计数,因为每个触发器可以存储一位数,选项B(4个)正确。

10. JK触发器具有多种功能,如置0、置1、保持和计数翻转,所以选项A是正确的。

11. 该题考察了逻辑函数的等价表达式,但没有提供具体的选项,无法直接给出答案,需要根据题目提供的函数进行推导。

12. 数字大小比较题,C选项(103)H转换为十进制是16进制的103,即10进制的163,是给定选项中最大的,所以C是最大数。

13. OC门电路(集电极开路门)的功能是输出高阻状态,当输入为高电平时,输出接地,使得连接到它的负载可以被外部信号控制,B选项符合其工作状态。

14. 组合逻辑电路不包含记忆功能,如编码器属于组合逻辑电路,而触发器、寄存器和计数器都包含时序逻辑元素,因此A选项正确。

15. 钟控RS触发器的约束条件是指其工作状态依赖于输入时钟信号,通常在时钟上升沿或下降沿触发状态改变,题干未给出具体条件,需要结合教材知识来填写。

这些题目涵盖了数字逻辑中的多个重要知识点,对于期末复习和巩固理论知识非常有帮助。

2009-12-12 上传

点击了解资源详情

2020-06-28 上传

2020-07-16 上传

2014-07-10 上传

2022-06-25 上传

2022-08-08 上传

2021-09-11 上传

2022-06-25 上传

Sir_Eric

- 粉丝: 4

- 资源: 3

最新资源

- sicherheit_ws:安全概念讲习班

- Bregman Cookbook:此工具箱提供基于 Bregman Iterations 的信号/图像/3D 处理-matlab开发

- 下一个大学

- fccWebDesign:在此仓库内,有我为在线课程(在freeCodeCamp上进行的响应式Web设计认证)制作的项目

- dchr.host:端到端K8s CICD练习

- 4ampr-fj2021-paginas-web-semana-03:专业人士

- Accuinsight-1.0.36-py2.py3-none-any.whl.zip

- vicms:用于python-flask的迷你内容管理架构

- Atcoder

- Pure

- irawansyahh.github.io:我的个人网站

- ask:一种在 Node 或浏览器中构建 HTTP 请求的简单、可链接的方式

- Dark Crystals New Tab Game Theme-crx插件

- 库存-REST-API:REST APIのテスト

- JavascriptVerletAlgorithm

- antiwasm:Web程序集objdump