FPGA时序分析精讲:TimeQuest静态时序模型与实战

"FPGA那些事儿--TimeQuest静态时序分析REV7.0"

本文档深入探讨了FPGA设计中的一项关键工具——TimeQuest静态时序分析器,这是Altera(现Intel FPGA) Quartus II软件中用于验证数字电路时序性能的重要组件。文档分为六个章节,详细介绍了TimeQuest的工作原理、模型构建、时序分析、约束设置以及与外部模型和物理时钟相关的概念。

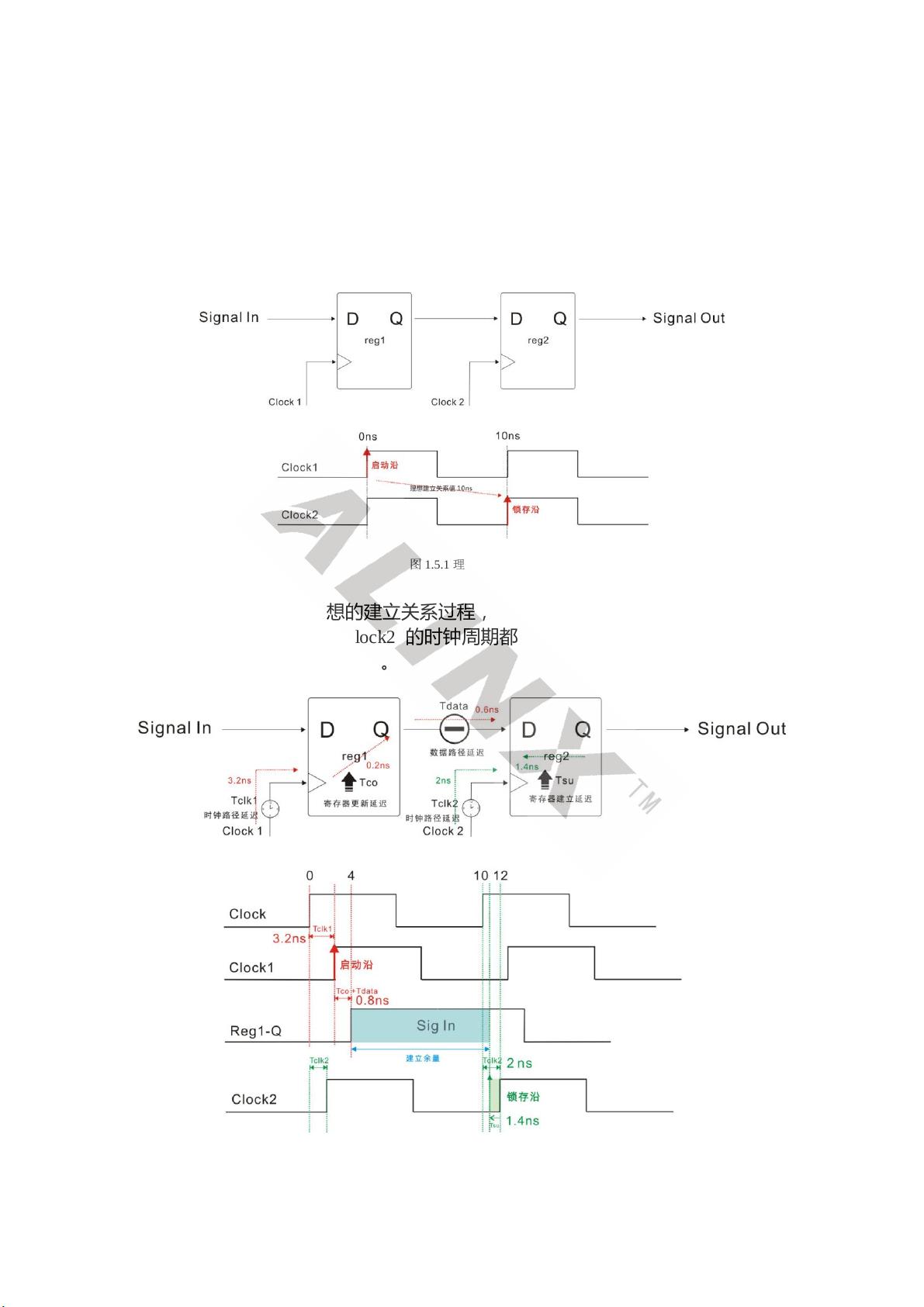

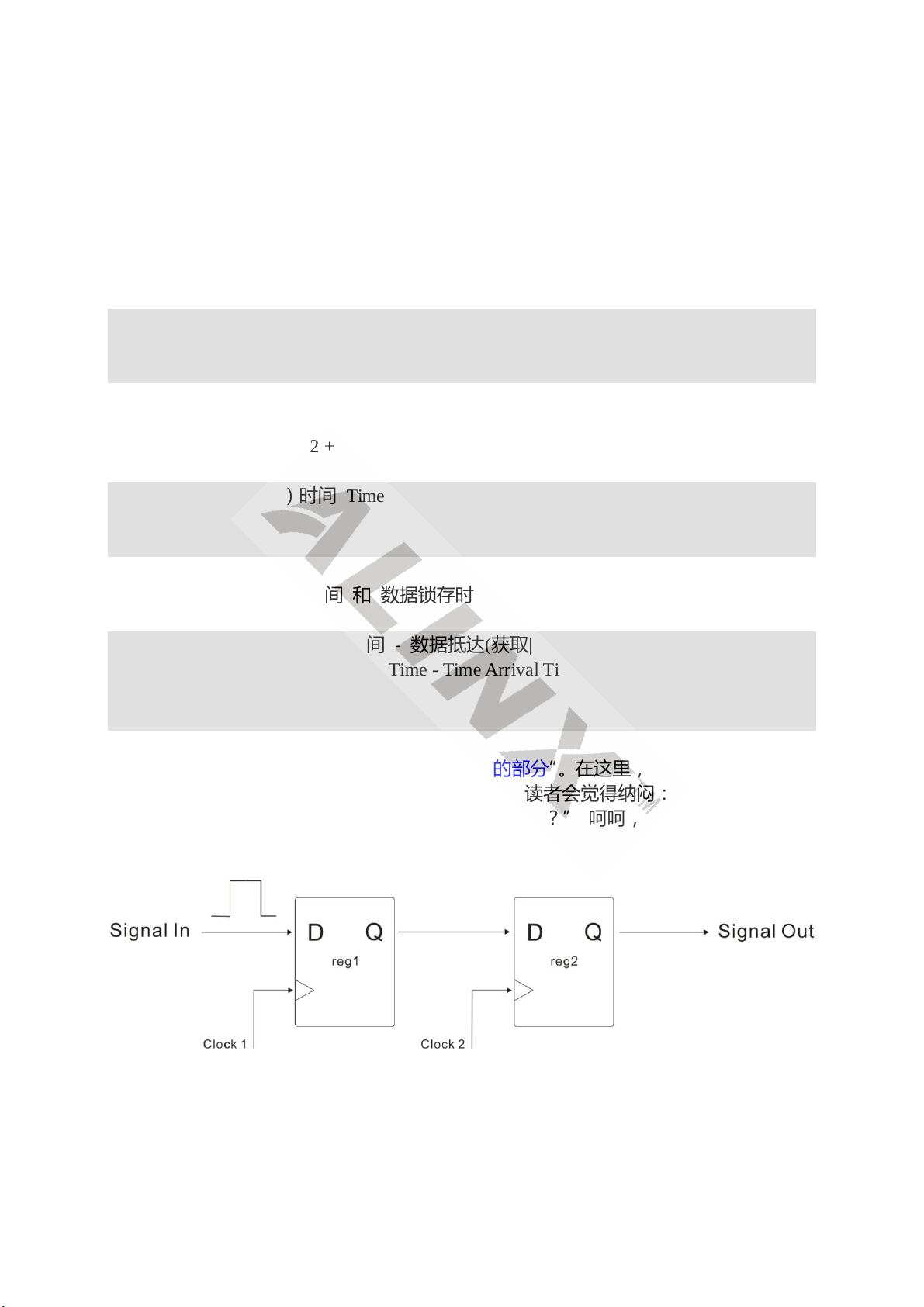

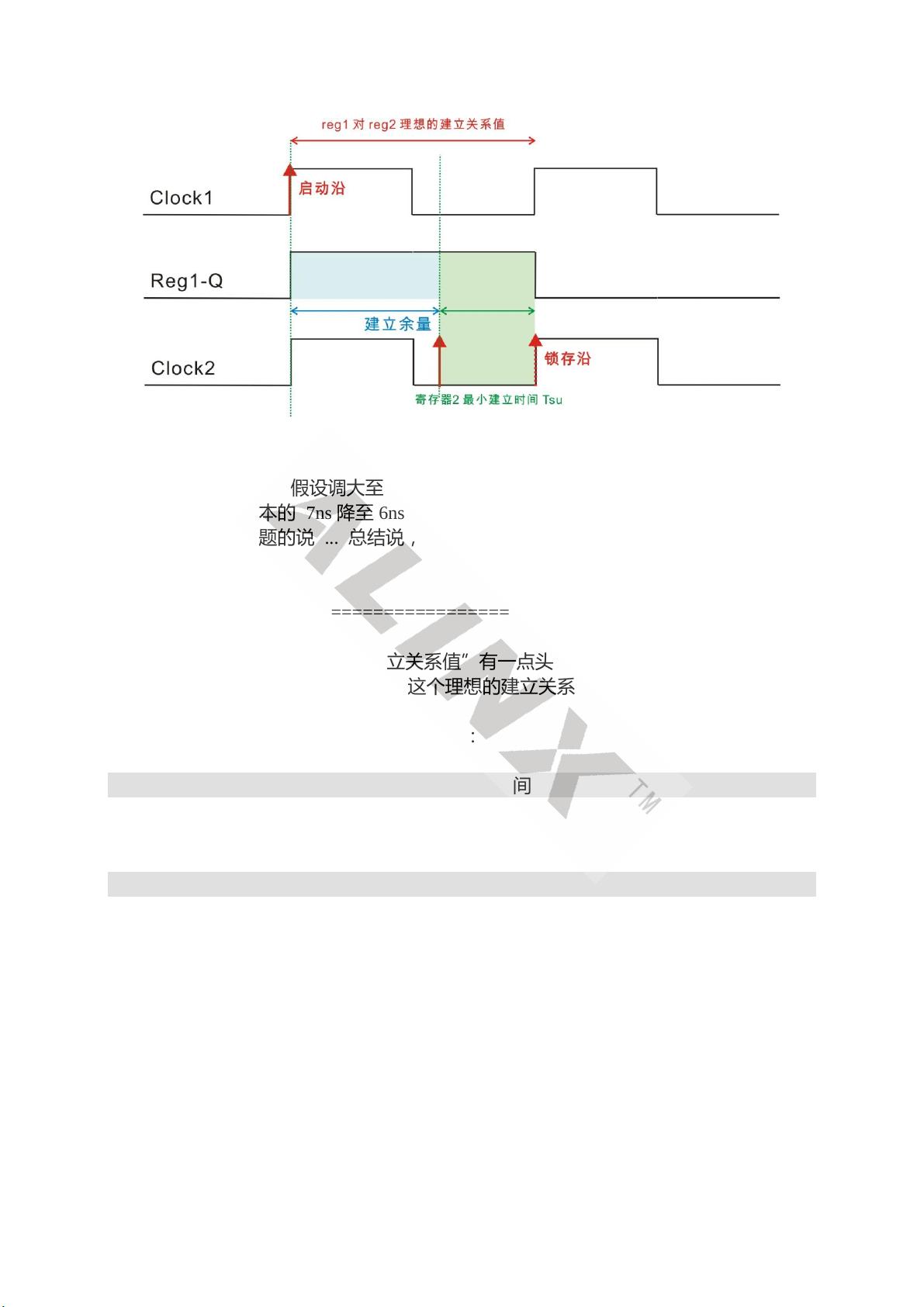

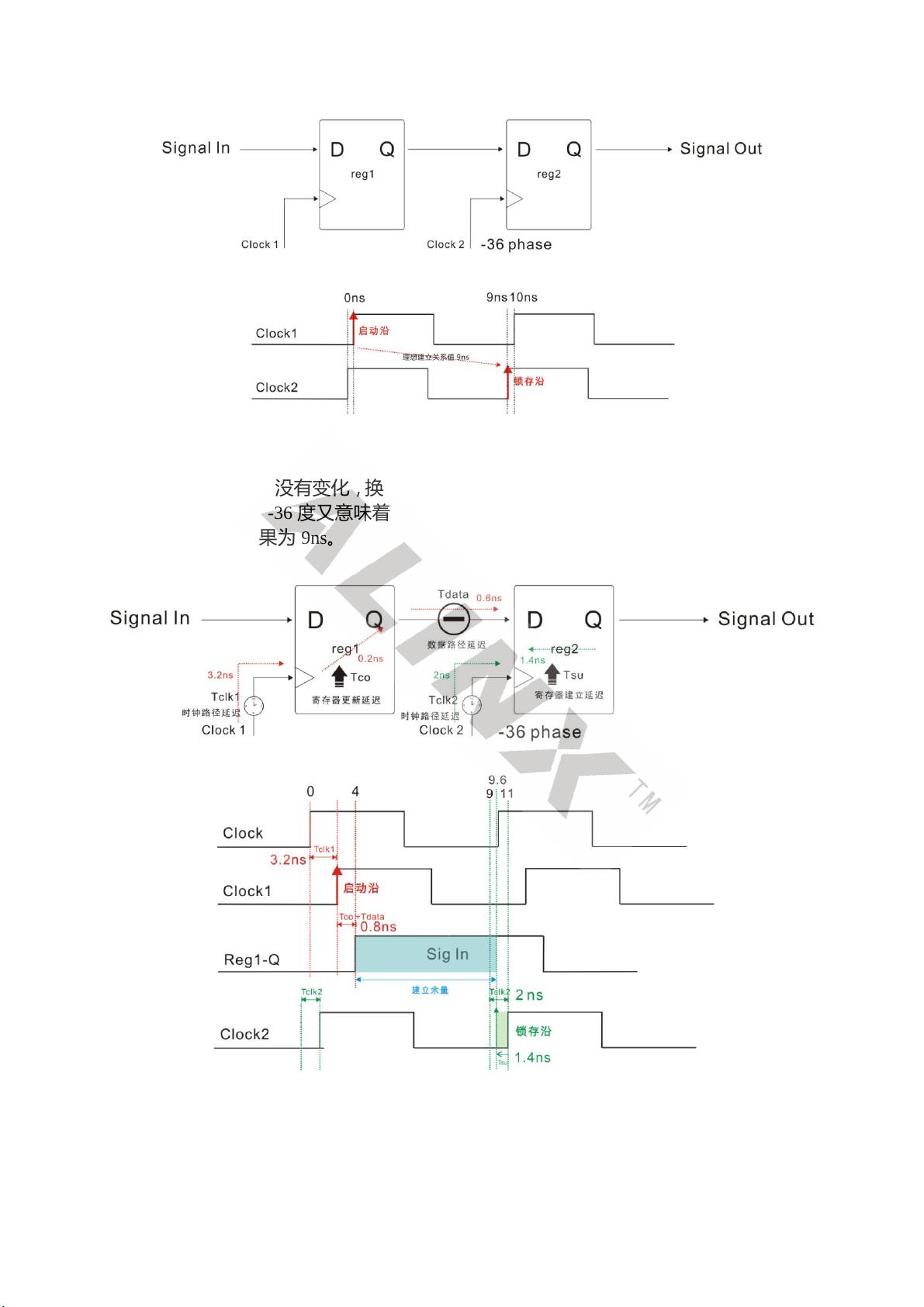

第一章介绍了TimeQuest的静态时序分析模型,包括模型的基础单位,如理想的建立和保持关系值。讨论了物理中的建立关系过程和建立余量,澄清了一些常见的误解,并分别详述了建立余量和保持余量的概念。

第二章关注TimeQuest模型的角色、网表概念以及时序报告的生成。通过实例展示了如何使用SDC(Synopsys Design Constraints)文件对设计进行约束,并解释了如何分析时序,设置时钟约束以及生成时序报告。

第三章是TimeQuest的基础知识扫盲,讲解了余量的概念,区分了内部和外部延迟因数,并探讨了不同层次的时间要求。此外,还介绍了如何创建和理解TimeQuest模型以及约束命令的行为。

第四章重点讨论了内部延迟,特别是与PLL(锁相环)相关的约束和时钟设置。通过一系列实验,如vga模块的物理时序分析,揭示了延迟怪兽(复杂延迟情况)的处理方法,以及如何合理使用SetMulticyclePath和SetFalsePath命令。

第五章探讨了网表质量和外部模型的影响。解释了Fmax评估值的含义,展示了如何理解和处理外部模型的输入/输出约束,以及如何推导外包数据的公式。

第六章深入到物理时钟的话题,包括如何向TimeQuest提供外部时钟的延迟信息,时钟抖动的影响,以及如何通过set_clock_latency命令处理这些因素。

整体来看,这份文档为FPGA设计者提供了TimeQuest静态时序分析的全面指南,涵盖了从基础理论到实际操作的各个环节,对于优化FPGA设计的时序性能具有重要的参考价值。

162 浏览量

2022-07-13 上传

656 浏览量

点击了解资源详情

144 浏览量

681 浏览量

417 浏览量

417 浏览量

yqjykn123

- 粉丝: 2

最新资源

- 网页自动刷新工具 v1.1 - 自定义时间间隔与关机

- pt-1.4协程源码深度解析

- EP4CE6E22C8芯片三相正弦波发生器设计与实现

- 高效处理超大XML文件的查看工具介绍

- 64K极限挑战:国际程序设计大赛优秀3D作品展

- ENVI软件全面应用教程指南

- 学生档案管理系统设计与开发

- 网络伪书:社区驱动的在线音乐制图平台

- Lettuce 5.0.3中文API文档完整包下载指南

- 雅虎通Yahoo! Messenger v0.8.115即时聊天功能详解

- 将Android手机转变为IP监控摄像机

- PLSQL入门教程:变量声明与程序交互

- 掌握.NET三层架构:实例学习与源码解析

- WPF中Devexpress GridControl分组功能实例分析

- H3Viewer: VS2010专用高效帮助文档查看工具

- STM32CubeMX LED与按键初始化及外部中断处理教程