CMOS晶体管布局艺术:设计与优化策略

需积分: 22 194 浏览量

更新于2024-07-26

收藏 2.14MB PDF 举报

《CMOS晶体管布局功夫:设计艺术》

本资源是一份关于CMOS(互补金属氧化物半导体)晶体管布局的专业技术文献,由Lee Eng Han、Valerio B. Perez、Mark Lambert Cayanes和Mary Grace Salaber共同撰写,版权日期为2005年。书中详细介绍了CMOS晶体管设计的关键步骤和技术,对于理解并优化集成电路版图设计具有重要意义。

首先,章节1是引言,概述了CMOS技术的基础和在电子工业中的核心地位。随着微电子技术的发展,合理的晶体管布局对于提高电路性能、功耗控制和集成度至关重要。

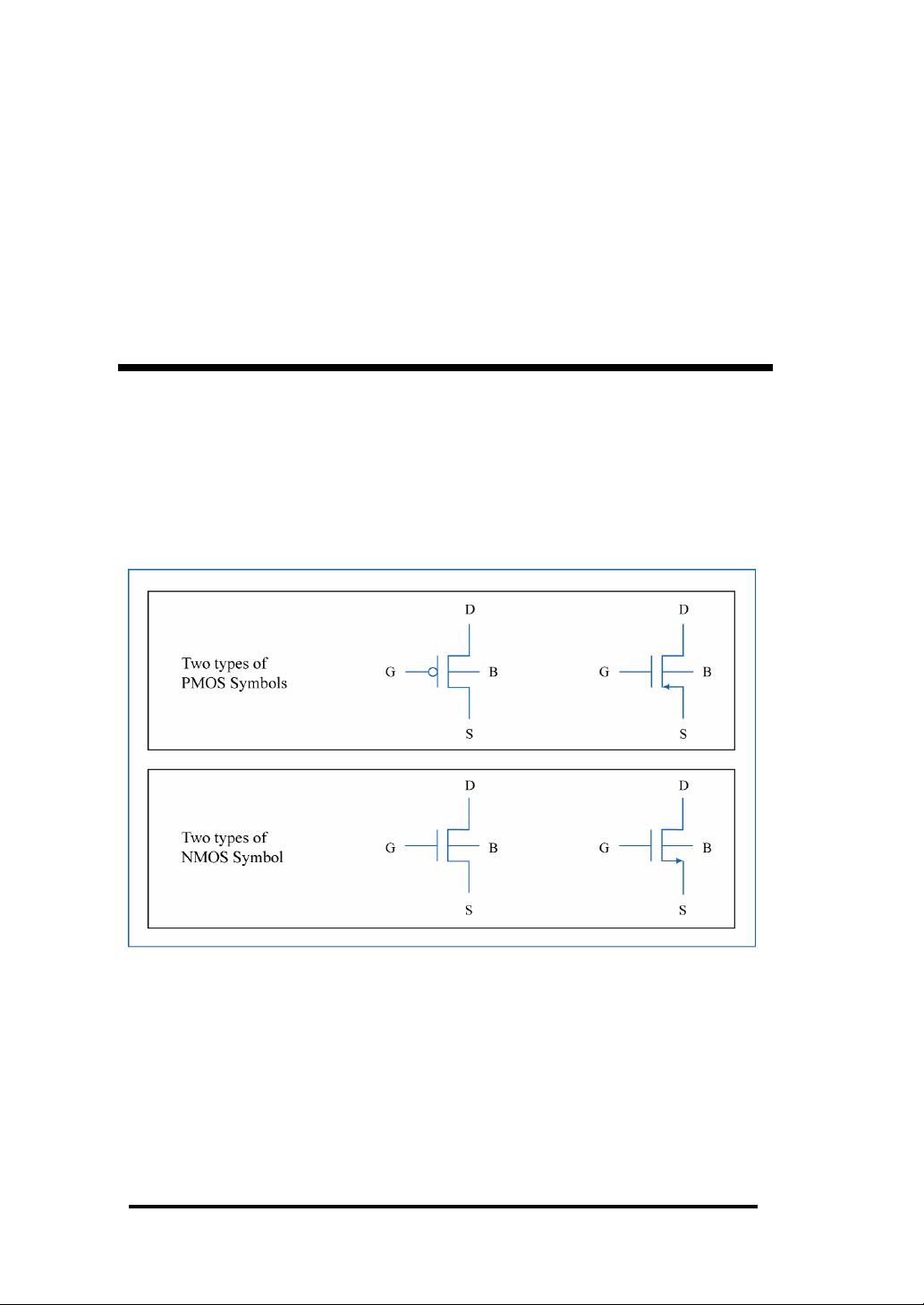

第二章深入探讨了MOS(Metal-Oxide-Semiconductor)晶体管的基本原理,包括其工作原理和结构,以及如何通过选择合适的器件参数来实现最佳性能。

第三章讲解了CMOS晶体管的制造过程,涵盖了从材料选择、光刻到后处理工艺的各个环节,以确保晶体管的可靠性和一致性。

接下来的五章分别聚焦于单个晶体管的布局技巧:

1. 第一阶段强调基本布局,确保基本的电荷传输路径清晰,减少寄生效应。

2. 第二阶段着重于紧凑设计,优化器件尺寸和形状以减小面积,提升密度。

3. 第三阶段关注速度提升,通过改进栅极和源/漏接触来改善开关速度。

4. 第四阶段讨论清理子电路干扰,确保信号完整性。

5. 第五章平衡面积、速度和噪声,追求高性能与低噪声的综合优化。

第六至第八章进一步扩展到多个晶体管的布局策略,包括:

6. 提高整体设计效率的复用方法。

7. 接近布局的考量,以减少互连线的影响。

8. 使用占位晶体管(dummy transistor)来改善电路布局的灵活性和一致性。

最后两章涉及更为细致的布局技术:

9. 接触间距管理,确保相邻器件间信号传输的高效性。

10. 交错布局(interdigitated layout),利用空间利用率和互耦效应的优势。

《CMOS Transistor Layout Kung Fu》提供了深入且实用的指导,涵盖了从理论到实践的全面内容,帮助工程师们在实际设计中灵活运用这些布局技巧,以提升电路性能和生产效率。

小马哥过河

- 粉丝: 3

最新资源

- React.js实现的简单HTML5文件拖放上传组件

- iReport:强大的开源可视化报表设计器

- 提升代码整洁性:Eclipse虚线对齐插件指南

- 迷你时间秀:个性化系统时间显示与管理工具

- 使用ruby-install一次性安装多种Ruby版本

- Logality:灵活自定义的JSON日志记录器

- Mogre3D游戏开发实践教程免费分享

- PHP+MySQL实现的简单权限账号管理小程序

- 微信支付统一下单签名错误排查与解决指南

- 虚幻引擎4实现的多边形地图生成器

- TouchJoy:专为触摸屏Windows设备打造的屏幕游戏手柄

- 全方位嵌入式开发工具包:ARM平台必备资源

- Java开发必备:30个实用工具类全解析

- IBM475课程资料深度解析

- Java聊天室程序:全技术栈源码支持与学习指南

- 探索虚拟房屋世界:house-tour-VR应用体验