基于VHDL的全数字锁相环设计:发展历程与实现详解

版权申诉

118 浏览量

更新于2024-06-29

收藏 1.37MB DOCX 举报

本文档深入探讨了基于VHDL的全数字锁相环(ADPLL)的设计,从锁相环的历史发展和全数字锁相环的兴起开始。1.1节介绍了锁相环(PLL)自1932年DeBellescize的"相关通信"概念起,经历了从模拟到数字的转变,特别提到了1965年出现的第一款PLL集成芯片,即线性PLL(LPLL),主要由模拟乘法器、RC滤波器和VCO构成。

随着技术的进步,PLL逐渐向全数字形式演进,这在1970年左右开始显现。全数字锁相环(ADPLL)通过数字信号处理技术,如数字鉴相器和数字滤波器,提供更高的精度和灵活性,适用于更广泛的频谱锁定和频率合成应用。

第二章详细阐述了全数字锁相环的开发系统,包括EDA(电子设计自动化)技术的发展,如FPGA(现场可编程门阵列)的应用,以及硬件设计语言VHDL的介绍。VHDL作为一种高级硬件描述语言,具有模块化、抽象和可读性强的特点,是设计和实现ADPLL的关键工具。MAX+PLUSII软件开发工具也在此部分被详细介绍,它支持整个设计流程,从设计到仿真和分析。

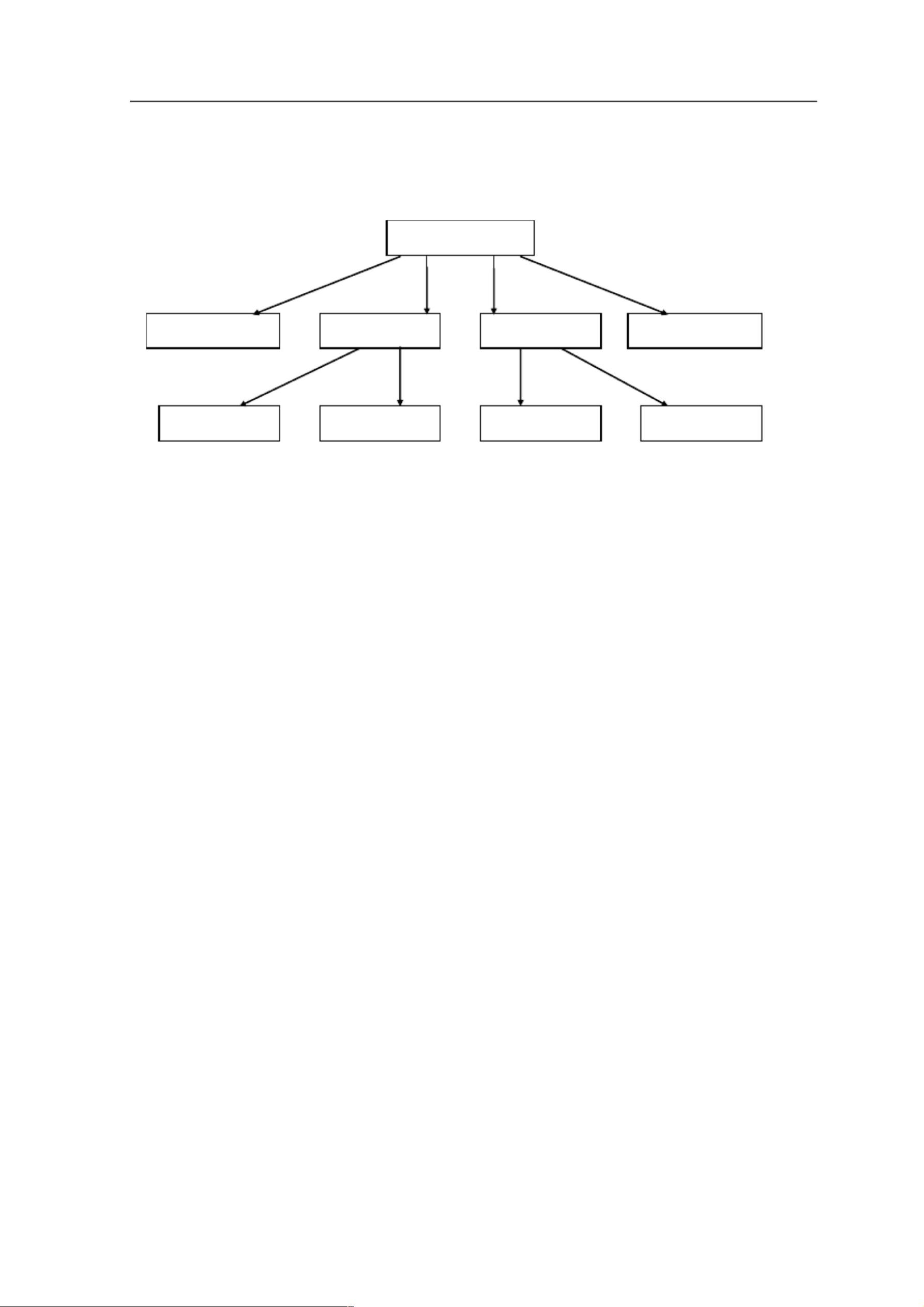

设计规划在第三章中展开,讨论了整体方案的选择,以及针对全数字锁相环的不同设计方案。章节还涉及设计团队的分工,强调了模块划分的重要性,为后续的VHDL设计提供了清晰的架构基础。

在第四章的核心部分,作者详细介绍了基于VHDL的全数字锁相环设计。首先,对ADPLL进行了全面的介绍,接着深入剖析了其结构和工作原理。然后,逐个模块地讲解了VHDL设计,包括基本结构框图的构建,各个模块的工作原理和子程序设计。这部分内容不仅涵盖了理论,还包括实际的系统性能分析,确保设计的实用性和有效性。

这篇文档通过丰富的历史背景和详细的技术解析,为读者呈现了一个从理论到实践的全数字锁相环设计过程,特别是在VHDL这一现代硬件设计工具的应用上,充分体现了其专业性和实用性。

2011-10-12 上传

2021-09-15 上传

2022-06-14 上传

2021-12-25 上传

2021-12-31 上传

2022-11-30 上传

2023-04-19 上传

xxpr_ybgg

- 粉丝: 6764

- 资源: 3万+

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍