Verilog入门:从基础到层次详解

需积分: 36 154 浏览量

更新于2024-07-18

收藏 1.63MB PDF 举报

Verilog HDL入门课程提供了一个全面的指导,旨在帮助初学者理解和掌握这种硬件描述语言。首先,课程介绍了Verilog HDL的基本概念,它是一种专门用于数字系统建模的语言,支持从算法级到开关级的不同抽象设计层次。Verilog由Gateway Design Automation公司创建,后被Cadence收购,并在1995年由IEEE标准化为IEEE Std 1364-1995(Verilog-1995),并在2001年更新为IEEE 1364-2001(Verilog-2001)。

与VHDL相比,虽然两者都是硬件描述语言,但VHDL更倾向于系统级设计,而Verilog则更适合电路级设计。C语言作为计算机程序设计语言,强调顺序执行,而Verilog的语法更接近C,但它的核心在于对硬件并发执行过程的建模,设计者需要理解并将其应用于实际电路设计。

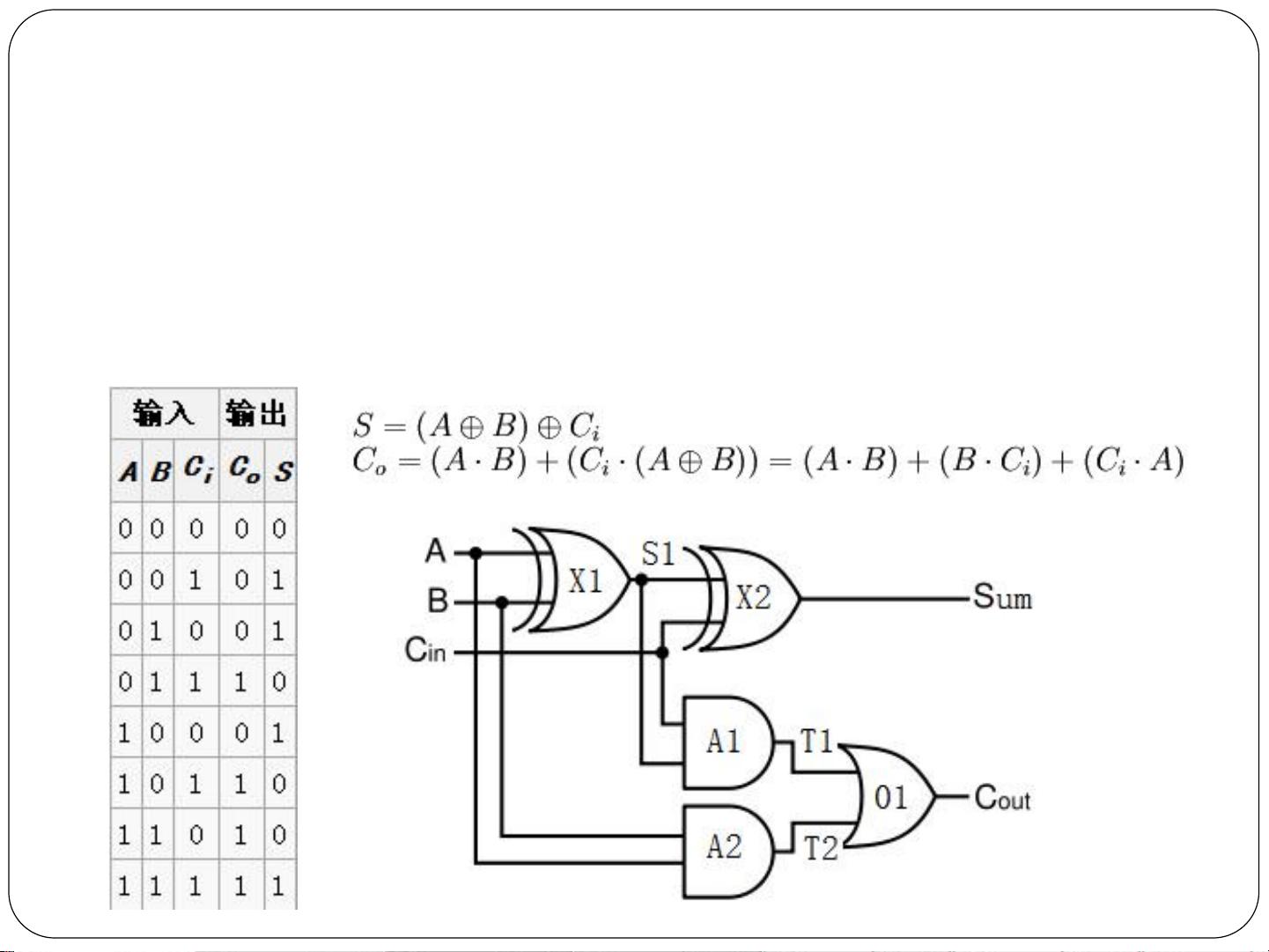

在抽象层次上,Verilog提供了四个关键级别:行为或算法级,关注设计者实现的逻辑,数据流级描述数据流在寄存器间的传输和处理;门级设计着重于逻辑门和它们的连接;而开关级则是最底层,直接使用开关和存储节点构建模块。此外,还提到了RTL级(寄存器传输级),这是设计过程中非常基础的一环,它关注的是模块内部的具体实现细节。

学习Verilog HDL,初学者需理解这些概念,并注意将语言运用到硬件电路的设计和验证过程中,以便更好地进行硬件描述和仿真。通过实践和理论相结合,逐渐提升在Verilog HDL中的编程能力,这对于电子工程、嵌入式系统和半导体设计等领域都至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-10-10 上传

2008-06-13 上传

2011-10-05 上传

2011-03-20 上传

2009-10-15 上传