FPGA实现的可调增益与10s语音存储的数字化回放系统设计

181 浏览量

更新于2024-08-30

1

收藏 359KB PDF 举报

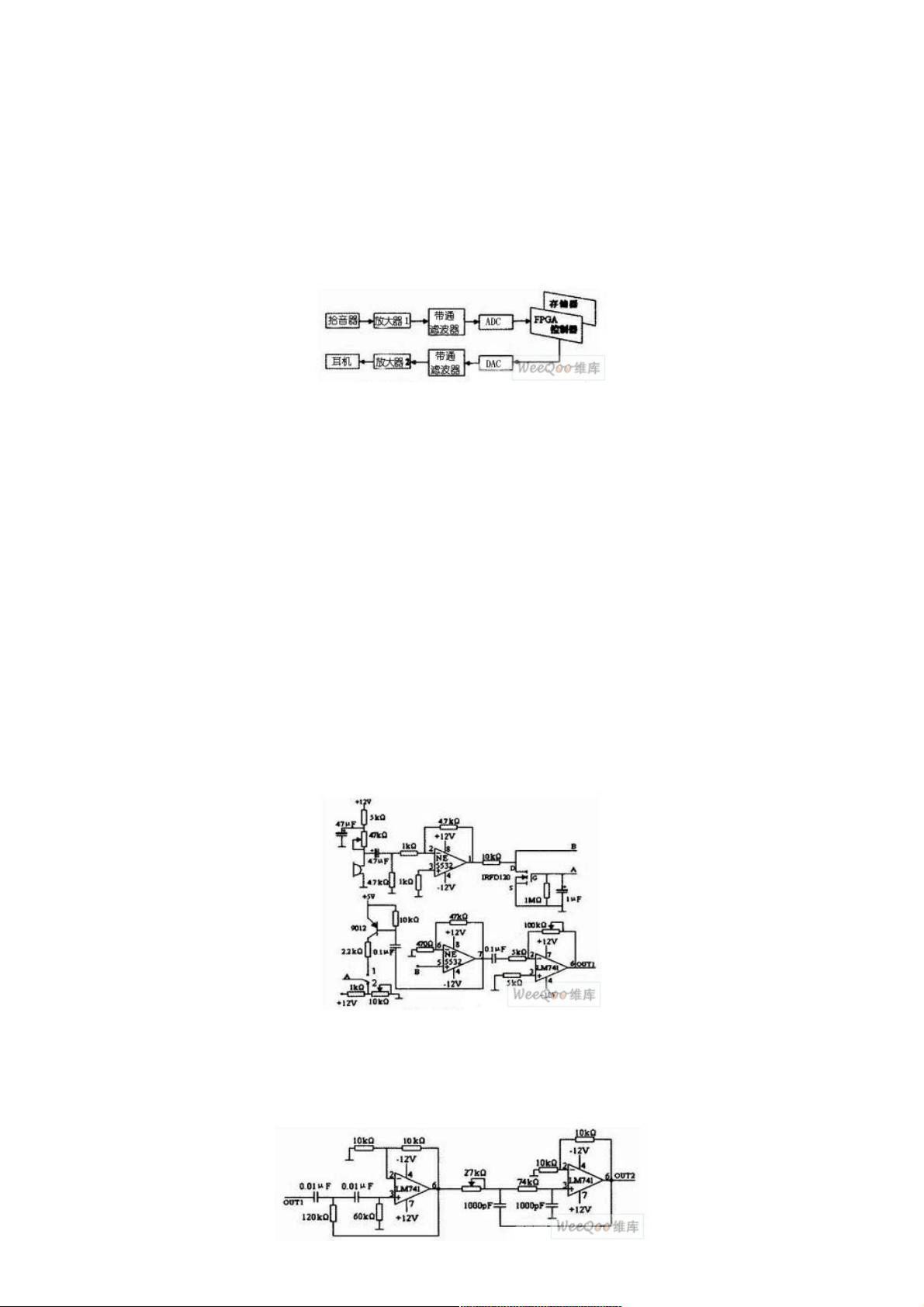

本文档主要介绍了基于FPGA的语音存储与回放系统的详细设计,该系统旨在满足特定的技术要求,包括信号处理和存储功能。以下是对关键知识点的详细解析:

1. **设计要求**

- 系统目标:设计一个数字化的语音存储与回放系统,采用FPGA作为核心处理器,避免使用单片语音专用芯片。

- 功能特性:

- 放大器1:具有46dB的可调增益,放大器2提供40dB增益,以确保信号强度。

- 带通滤波器:通带范围为300Hz至3.4kHz,用于去除噪声和不必要的频率成分,保持语音信号质量。

- ADC(模数转换器):采样频率为8kHz,8位分辨率,保证足够的音频细节捕捉。

- 存储时间:要求语音至少可以存储10秒。

- DAC(数模转换器):转换频率与ADC相同,也为8kHz,输出质量良好。

- 质量标准:回放的语音应无失真,声音清晰。

2. **硬件电路设计**

- **放大器1**:音频信号首先通过级联放大器,IRD120负责自动或手动增益控制,通过场效应管实现可变电阻控制。

- **带通滤波器**:采用定制的滤波器,确保信号的300Hz~3.4kHz范围内无失真,提高信号纯净度。

- **ADC电路**:使用ADC0809,采样速度为8kHz,100μs转换时间,将模拟音频信号转换为数字数据。

- **语音存储电路**:利用HM628128D存储芯片,存储数字化的语音数据,该芯片的接口需按照电路图进行连接。

- **DAC电路**:数模转换器用来将存储的数字数据恢复成模拟信号,回放时保持原始的8kHz频率和8位精度。

这个设计不仅涵盖了从音频输入到存储再到输出的完整流程,还强调了FPGA在系统中的重要作用,以及对关键组件性能的精确控制。这样的系统在音频处理和存储应用中具有较高的实用价值,特别是在需要灵活配置和高音质再现的场合。

2020-10-25 上传

2015-04-12 上传

2021-09-25 上传

2020-11-03 上传

2021-07-13 上传

点击了解资源详情

2020-08-05 上传

2021-01-19 上传

2021-01-19 上传

weixin_38627521

- 粉丝: 5

- 资源: 924

最新资源

- taro-fast-framework-main.zip

- Wildcard_Plugin:删除CF的通配符插件

- 基于Asp.net的温岭家乡网站设计作业源码

- Python库 | jgf-0.2.1-py3-none-any.whl

- tsuru-stress-app:一个简单的应用程序来强调tsuru

- progress-maven-plugin:Maven Reactor 进展

- UyarValluvam

- 基于Zernike多项式进行波面拟合研究_张伟_拟合_多项式_zernike_

- HuffmanCode.rar_/资料_C/C++__源码/资料_C/C++_

- Photocopier:从Mac版Chrome复制常规图像_和_ GIF动画

- springboot052旅游管理系统的设计与实现_zip.zip

- This is a code for New Year's Day Countdown

- Python库 | je_editor-0.0.11-py3-none-any.whl

- 520表白代码,你值得拥有

- Project-1:随机报价生成器

- omniauth-pam:OmniAuth的PAM策略