Verilog-HDL设计编码器和译码器实验指南

需积分: 16 59 浏览量

更新于2024-07-21

收藏 496KB DOC 举报

"该文档是针对大学生数学电路模拟课程的实验指导书,专注于使用Verilog-HDL语言设计编码器和译码器的实践教学。实验旨在让学生熟悉QuartusII的编程环境,掌握Verilog-HDL语言,以及软件仿真、编程下载和硬件测试流程。书中详细介绍了编码器和译码器的原理,包括普通编码器和优先编码器,并提供了具体的Verilog-HDL程序示例。"

实验七的主要目标是让学生通过实际操作来巩固理论知识,包括:

1. 熟练使用QuartusII集成开发环境,掌握Verilog-HDL代码的编写和输入。

2. 学会如何进行软件仿真,将设计的代码编程下载到FPGA(Field-Programmable Gate Array)中,以及如何进行硬件测试验证。

3. 掌握编码器和译码器的Verilog-HDL设计方法,理解这两种基本逻辑电路的功能和实现方式。

4. 特别地,学习7段数码显示译码器的设计,这对于理解和应用实际数字电路显示系统至关重要。

预习部分要求学生事先了解和掌握:

1. QuartusII的工作界面和Verilog-HDL的文本编辑。

2. 实验中的仿真流程,包括建立模型、运行仿真并观察结果。

3. 编程下载步骤和硬件测试的基本操作。

4. 自行编写编码器和译码器的Verilog-HDL代码,以提升编程能力。

实验内容深入探讨了编码器和译码器的基本概念:

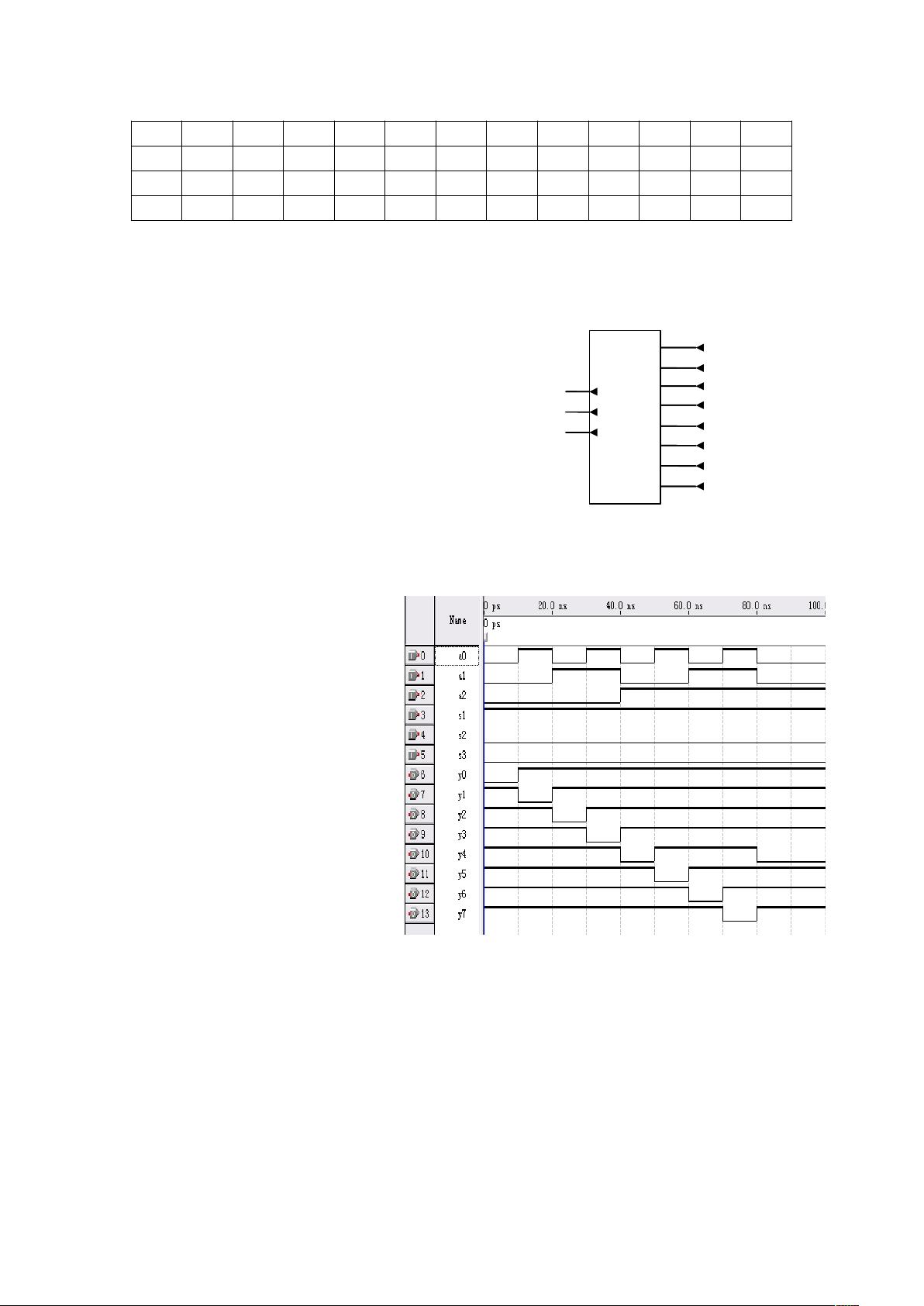

编码器是将多个输入信号转换为一个或多个二进制输出的逻辑电路,分为普通编码器和优先编码器。普通编码器在任何时刻只有一个输入有效,否则会导致输出混乱。例如,8线-3线普通编码器有8个输入(I0~I7),当其中一个输入为高电平时,输出Y2、Y1、Y0构成3位二进制编码。书中给出了8种可能的输入与输出的对应关系。

在Verilog-HDL中,编码器可以被描述为一个模块,例如示例1展示了一个8线-3线普通编码器的实现。通过定义输入输出端口,使用always块的case语句来根据输入值设置输出状态。这种描述方式简洁明了,便于代码复用和硬件实现。

此外,译码器则是将一个或多个二进制输入转换为多个输出的逻辑电路,常用于驱动显示器或控制其他逻辑单元。7段数码显示译码器就是一个典型的例子,它将二进制数字转换为能够驱动7段LED显示器的输出信号,以便显示十进制数字。

通过这个实验,学生不仅能掌握Verilog-HDL语言的编程技巧,还能深入了解编码器和译码器的工作原理,增强数字逻辑设计的实际操作能力。这为他们未来在数字系统设计、嵌入式系统开发等领域的工作奠定了坚实的基础。

2022-06-16 上传

2010-10-15 上传

2024-11-08 上传

2023-05-22 上传

2023-11-05 上传

2023-05-24 上传

2024-10-26 上传

2024-09-24 上传

qq_33088547

- 粉丝: 0

- 资源: 1

最新资源

- PureMVC AS3在Flash中的实践与演示:HelloFlash案例分析

- 掌握Makefile多目标编译与清理操作

- STM32-407芯片定时器控制与系统时钟管理

- 用Appwrite和React开发待办事项应用教程

- 利用深度强化学习开发股票交易代理策略

- 7小时快速入门HTML/CSS及JavaScript基础教程

- CentOS 7上通过Yum安装Percona Server 8.0.21教程

- C语言编程:锻炼计划设计与实现

- Python框架基准线创建与性能测试工具

- 6小时掌握JavaScript基础:深入解析与实例教程

- 专业技能工厂,培养数据科学家的摇篮

- 如何使用pg-dump创建PostgreSQL数据库备份

- 基于信任的移动人群感知招聘机制研究

- 掌握Hadoop:Linux下分布式数据平台的应用教程

- Vue购物中心开发与部署全流程指南

- 在Ubuntu环境下使用NDK-14编译libpng-1.6.40-android静态及动态库