基于FPGA的UART核心功能实现与优化

191 浏览量

更新于2024-09-04

收藏 219KB PDF 举报

"EDA/PLD中的一种基于FPGA的UART 电路实现"

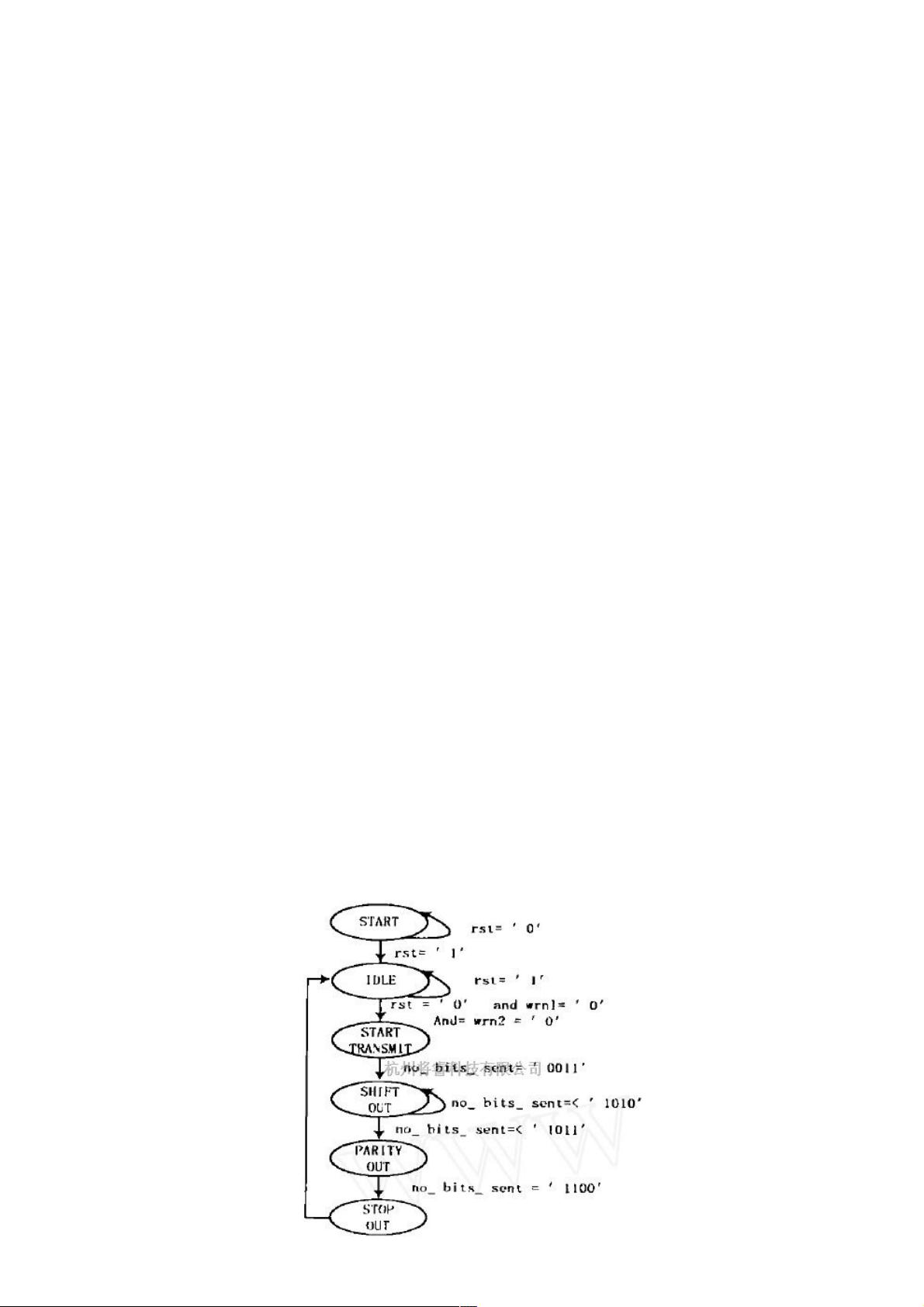

本文探讨了在EDA(电子设计自动化)和PLD(可编程逻辑器件)领域中,如何使用FPGA(现场可编程门阵列)来实现UART(通用异步收发传输器)的核心功能。传统的UART通常依赖于专门的集成电路,但在某些特定应用中,如多串口设备或加密通信,这种全功能的UART可能并不理想。设计者选择Xilinx的FPGA,将UART的关键模块内嵌入FPGA,这不仅能够满足异步通信的基本需求,还能提高电路的紧凑性、稳定性和可靠性。

UART是一种常见的串行通信接口,广泛应用于各种数据传输场景。其工作原理是在字符间无固定时间间隔的情况下,逐个传输数据,每个字符由起始位、数据位、校验位和停止位组成。起始位是低电平,数据位通常为5到8位,接着是校验位,最后是停止位,一般为1位、1位半或2位,均以高电平结束。这样的设计确保了接收端可以通过检测下降沿识别新的字符开始。

在FPGA实现的UART设计中,关键组成部分包括:

1. **数据总线接口**:连接微处理器和其他系统组件,负责数据的输入输出。

2. **控制逻辑和状态接口**:处理UART的工作模式,如发送、接收、中断请求以及错误检测等状态的管理。

3. **波特率发生器**:生成数据传输的时钟速率,确保收发双方同步。

4. **发送部分**:负责将并行数据转换为串行数据,添加起始位、校验位和停止位,然后通过串行接口发送出去。

5. **接收部分**:接收串行数据,检测起始位,校验数据,然后将数据转化为并行格式供系统使用。

使用FPGA实现UART的优势在于定制化程度高,可以根据具体需求裁剪或扩展功能,比如在多串口设备中,可以设计多个独立的UART通道。同时,由于FPGA的并行处理能力,可以实现实时的高速数据传输。此外,FPGA的可重配置特性使得在设计过程中能够方便地进行修改和优化,增加了设计的灵活性。

总结来说,本文提供的FPGA实现的UART电路设计,为那些需要高效、紧凑、可定制串行通信解决方案的项目提供了新的思路。通过这种方法,可以有效地减少硬件成本,提高系统的整体性能,并且在需要加密或其他特殊功能时,FPGA的可编程性使其成为理想的解决方案。

2020-11-05 上传

2020-11-06 上传

2023-12-30 上传

2023-05-05 上传

2023-08-18 上传

2024-01-18 上传

2024-06-30 上传

2023-06-03 上传

2023-10-29 上传

weixin_38650066

- 粉丝: 5

- 资源: 908

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展