2011-2013 Microchip Technology Inc. DS80000533G-page 5

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X

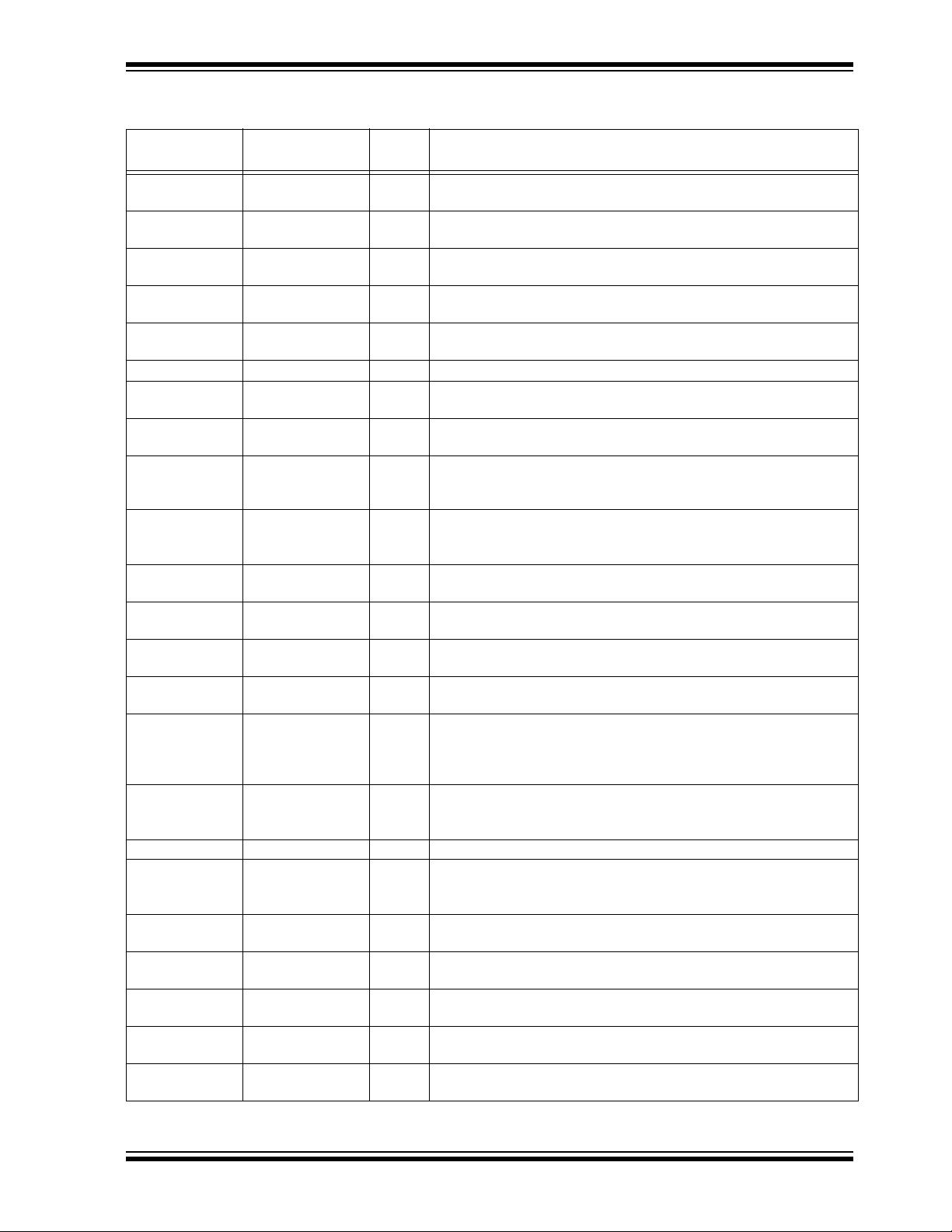

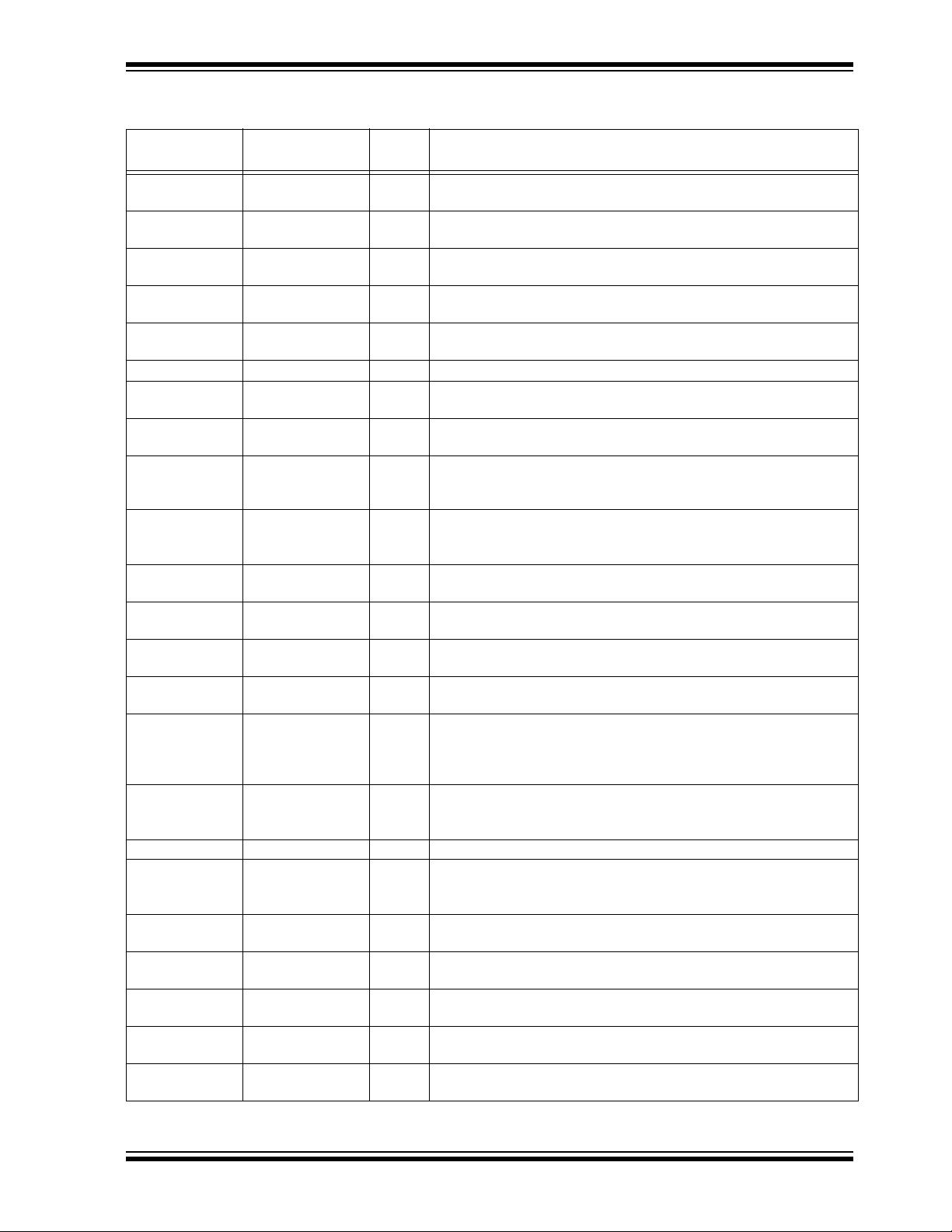

TABLE 2: SILICON ISSUE SUMMARY

Module Feature

Item

Number

Issue Summary

CPU div.sd 1. When using the div.sd instruction, the overflow bit is not getting set

when an overflow occurs.

CPU DO Loop 2. PSV access, including table reads or writes in the last instruction of a

DO loop is not allowed.

SPI Frame Sync Pulse 3. Frame Sync pulse is not generated in Master mode when FRMPOL

= 0.

SPI Frame Sync Pulse 4. When in SPI Slave mode, with the Frame Sync pulse set as an input,

FRMDLY must be set to ‘0’.

UART TX Interrupt 5. A Transmit (TX) interrupt may occur before the data transmission is

complete.

Power System Flash Regulator 6. The VREGSF (RCON<11>) bit always reads back as ‘0’.

ADC DONE bit 7. The ADC Conversion Status bit (DONE) does not work when an

external interrupt is selected as the ADC trigger source.

PTG Strobe Output 8. Strobe output pulse width is incorrectly dependent on the

PTGPWD<3:0> (PTGCON<7:4>) bit settings.

Op Amp Enabling Op Amp

mode

9. When using any of these Op Amp modules, or Analog Channels

AN0, AN3 or AN6, to sample external signals, bit

11 of the CMxCON

register must be set to ‘1’.

Op Amp AC/DC Electrical

Characteristics

10. The AC/DC electrical characteristics for the Op Amp module (and

the related ADC specifications) are not within the specifications

published in the current data sheet.

PWM Dead-Time

Compensation

11. Dead-Time Compensation is not enabled for Center-Aligned PWM

mode.

Flash Flash Programming 12. The stall mechanism may not function properly when erasing or

programming Flash memory.

QEI Index Counter 13. The QEI Index Counter does not count correctly in Quadrature

Detector mode.

QEI Modulo Mode 14. Modulo mode functionality is incorrect when the Count Polarity bit is

set.

PWM Master Time Base

Mode

15. In Master Time Base mode, writing to the period register, and any

other timing parameter of the PWM module, will cause the update of

the other timing parameter to take effect one PWM cycle after the

period update is effective.

ADC 1.1 Msps Sampling 16. Selecting the same ANx input (AN0 or AN3) for CH0 and CH1 to

achieve a 1.1 Msps sampling rate results in erroneous readings for

CH1.

ADC Channel Scan 17. Channel scanning is limited to AN0 through AN15.

Output Compare Interrupt 18. Under certain circumstances, an output compare match may cause

the Output Compare Interrupt Flag (OCxIF) bit to become set prior to

the Change-of-State (COS) of the OCx pin.

ECAN™ DMA 19. Write collisions on a DMA-enabled ECAN™ module do not generate

DMAC error traps.

PWM Immediate Update 20. Dead time is not asserted when PDCx is updated to cause an

immediate transition on the PWMxH and PWMxL outputs.

PWM Center-Aligned

Mode

21. PWMxH is asserted for 100% of the PWM period in Complementary

mode under certain circumstances.

PWM Complementary

Mode

22. With dead time greater than zero, 0% and 100% duty cycle cannot

be obtained on PWMxL and PWMxH outputs.

CPU Program Memory 23. Address error trap may occur while accessing certain program

memory locations.