四人表决器与两位加法器的FPGA实现

需积分: 20 142 浏览量

更新于2024-08-26

收藏 837KB DOC 举报

“表决器等数电实验.doc”文档主要涵盖了三个数字电子技术实验项目,分别是四人表决器的设计、两位加法器的设计和数值比较器的设计。每个项目都包含了电路设计、仿真波形分析以及FPGA器件的选择和管脚分配。

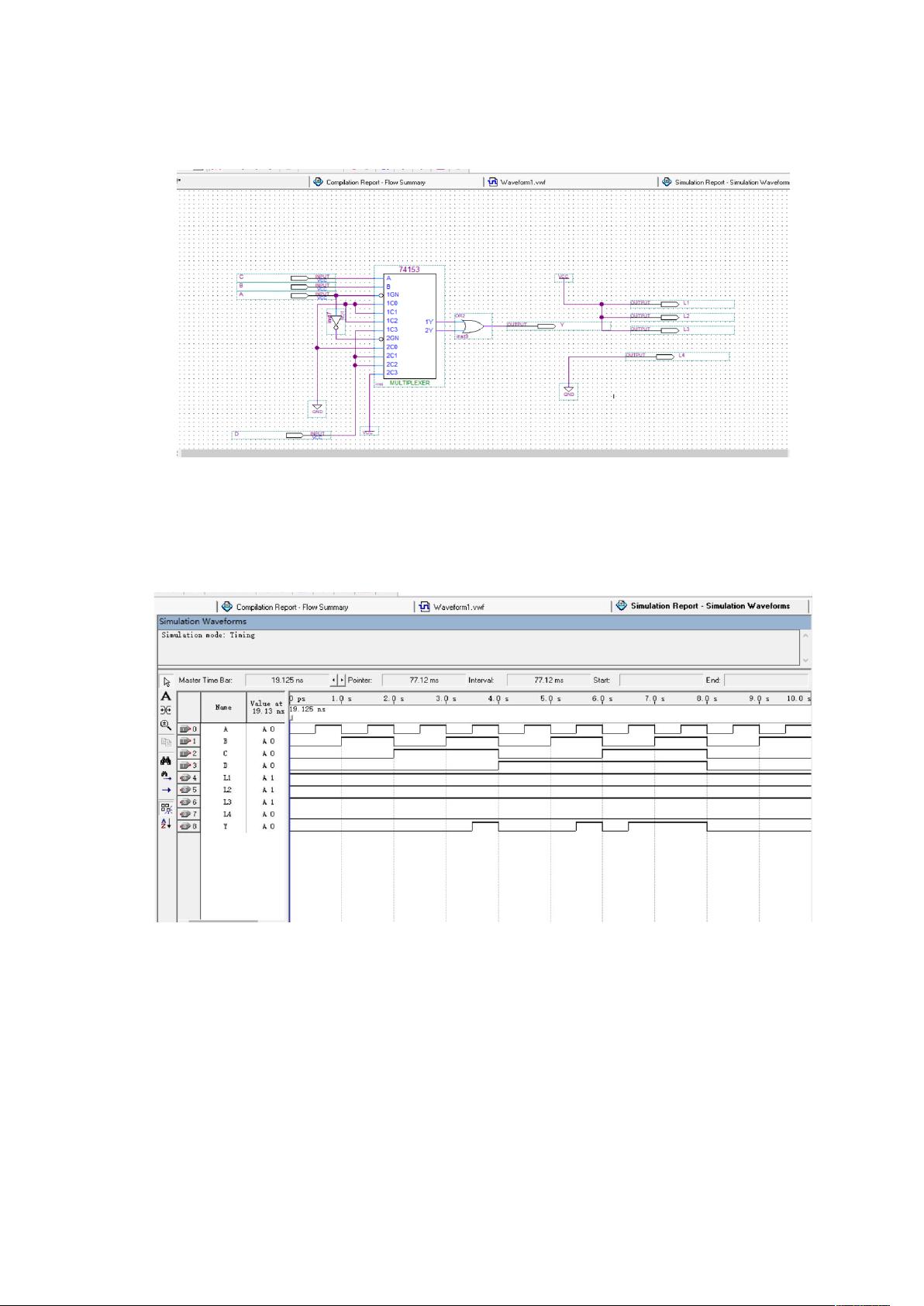

1. 四人表决器的设计:

- 电路逻辑表达式为Y=A’BCD+AB’CD+ABC’D+ABCD’+ABCD,表示只有当超过半数(三人)同意时,输出Y为高电平,表示表决通过。

- 使用了一个74153双四选一数据选择器,通过设置输入使能端实现所需逻辑功能。

- 仿真波形验证了电路功能,例如在3.5~4s时,当A、B、C为高电平时,D为低电平,输出Y为高电平,表明多数人同意,表决通过。

- FPGA器件选用Altera公司的CycloneII系列EP2C5Q208C8,具体管脚分配如文所述。

2. 两位加法器的设计:

- 输入为A1A0和B1B0,Cin为进位输入,输出为COS1S0,其中CO为进位输出,S1S0为二进制和。

- 电路分为两部分,上半部分处理高位相加,下半部分处理低位相加并结合进位信号。

- 波形图展示了不同输入情况下正确执行加法运算的例子,如在3.5~4s时,A1A0=11,B1B0=01,输出COS1S0=100,符合加法器的工作原理。

- FPGA管脚分配同样详细列出,便于实际硬件实现。

3. 数值比较器的设计:

- 模块接收两个两位二进制数A1A0和B1B0,输出G、Y、R分别表示A是否大于、等于或小于B。

- 缺少这部分的具体程序代码,但通常会包含条件判断,比如通过异或和与运算来比较每位数字的大小。

这些实验旨在帮助学习者掌握数字电子技术中的基本逻辑门电路、组合逻辑电路和时序逻辑电路的设计方法,以及FPGA编程和硬件实现。通过这些实验,学生可以加深对数字系统工作原理的理解,提高动手能力和问题解决能力。

2021-10-10 上传

2021-10-10 上传

2021-10-06 上传

2022-11-01 上传

2021-10-12 上传

2021-09-10 上传

2022-06-16 上传

weixin_52366295

- 粉丝: 0

- 资源: 5

最新资源

- 王珊 高等教育出版社 数据库第四版答案

- .net 软件自动化测试之道 pdf (.net平台下自动化测试必备之资料,精!!)

- 基于模糊预测算法的ATO仿真研究

- 3g技术讲解通信工程

- c#各种排序算法大全

- Cognos8.4新增功能优势说明

- JAVA基础面试题部分参考

- 段程序保存为文件名为Test.java的文件

- 影碟出租管理信息系统

- JAVA的学习笔记及开发模式

- Learning Oracle PL-SQL [O'Reilly, 524s, 2001r].pdf

- flash 适合于初学者的程序设计教程

- Visual C++开发工具与调试技巧整理

- 操作系统中的银行家算法

- Redhat Linux 9教学讲义

- RSVP协议端到端QOS控制机制的研究