优化ASIC和SoC嵌入式存储:存储器IP选择策略

165 浏览量

更新于2024-08-31

收藏 297KB PDF 举报

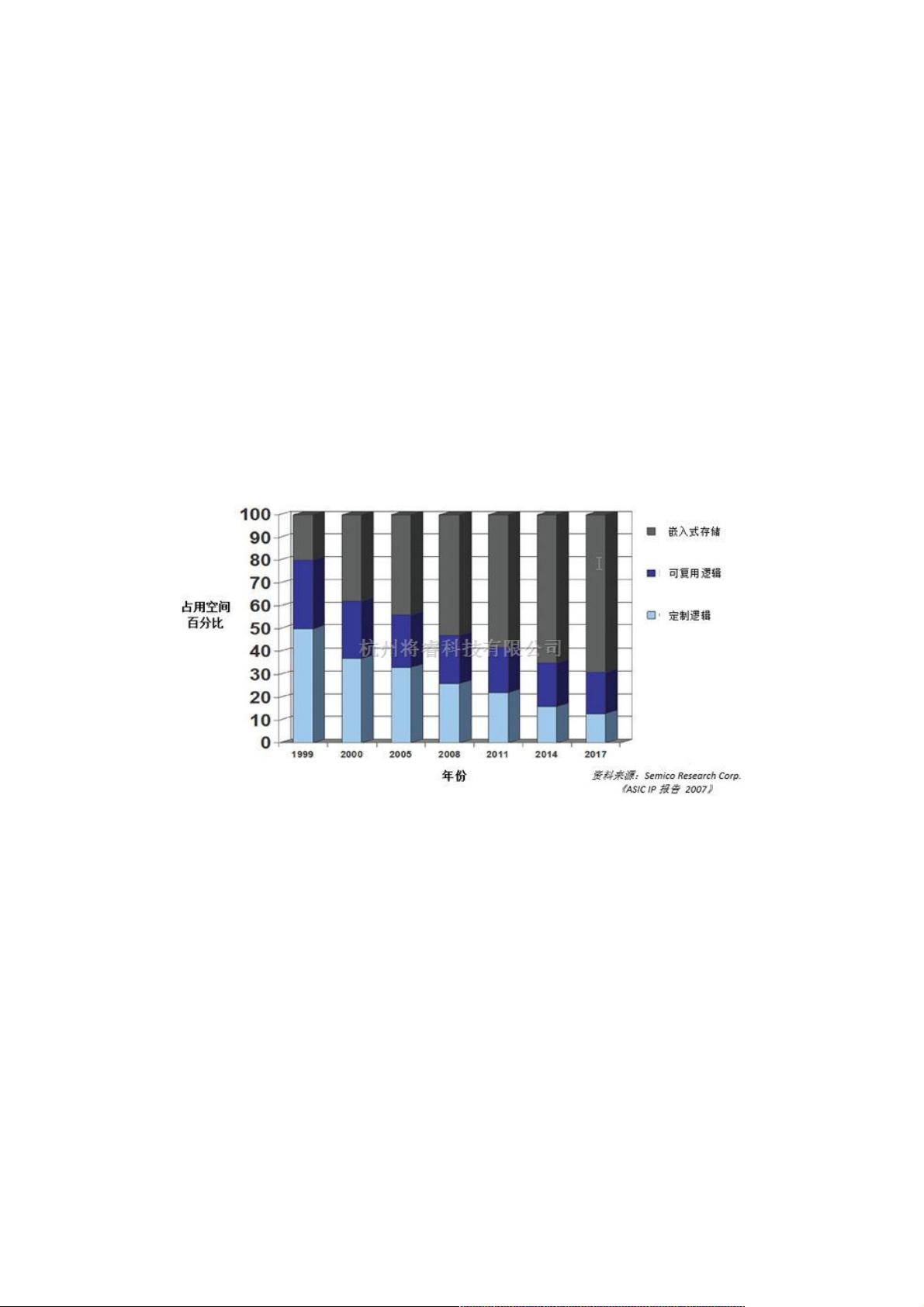

在现代嵌入式系统和ARM技术驱动的ASIC(专用集成电路)及SoC(系统级芯片)设计中,选择最优的嵌入式存储器IP是至关重要的。随着技术的发展,芯片的物理空间分配发生了显著变化。在过去的设计中,芯片通常被划分为定制逻辑区、可复用逻辑区(包括第三方IP和内部IP)和嵌入式存储区域。定制逻辑用于满足产品的独特功能,而可复用逻辑区域如USB、以太网和CPU核等保持相对稳定,但嵌入式存储器的需求随着市场对高速、多样化的无线通信标准(如802.11n和蓝牙)支持的增加而急剧增长。

据Semico Research 2013年的数据,现在的SoC和ASIC设计中,嵌入式存储器占据了超过50%的芯片空间,这表明存储器已成为设计中不可或缺的部分。嵌入式存储器的选择不仅关乎空间效率,还直接影响到系统的性能指标,如速度、功耗、密度和非易失性存储能力。为了优化这些性能,设计师必须考虑以下五个关键驱动因素:

1. 功率消耗:低功耗是嵌入式系统设计的重要考量,特别是在电池供电设备中,降低存储器的功耗能延长设备的使用寿命。

2. 速度:快速的数据访问对于实时处理和响应能力高的应用至关重要,如自动驾驶系统和物联网设备。

3. 可靠性和良率:高可靠性的存储器能减少故障率,确保系统的稳定性。

4. 密度:随着设备尺寸的减小,存储器的密度提升可以节省空间,提高集成度。

5. 成本:尽管高性能存储器可能带来初期投资成本,但在长期运行和总体系统成本上,合理的选择可能更具经济效益。

因此,设计师需要根据具体的应用需求和系统特性,通过综合权衡这些因素,选择最合适的嵌入式存储器IP。存储器编译器等工具可以协助这个过程,自动生成经过性能优化的存储器设计,以适应不断变化的技术趋势和市场需求。在ARM技术的背景下,选择合适的存储器IP对于打造高效、灵活和成本效益高的嵌入式系统至关重要。

164 浏览量

113 浏览量

122 浏览量

185 浏览量

153 浏览量

112 浏览量

185 浏览量

192 浏览量

117 浏览量

weixin_38659311

- 粉丝: 5

- 资源: 892

最新资源

- PRO-C-27约束身体

- 高斯白噪声matlab代码-GalaxyGAN:银河

- iwms正式版 .Net2.0_新闻文章发布系统.rar

- readmalanew.zip_MALA_gpr mala matlab_mala探地雷达_探地雷达_探地雷达 matlab

- JS-square-number-trainer:HTML,CSS,JS,QUERY

- Tragic

- 同步压缩小波变换matlab相关程序.zip

- goQuality-dev-contents:{收集高质量的开发内容}

- lwc-modal:用于Salesforce.com(SFDC)的Lightning Web Components(LWC)系统的可访问,可组合模式

- CMPT-120L-902-21S

- 自定义视图可使用单击按钮或滑动从给定范围内选取一个值。-Android开发

- kalman.zip_SOC Kalman_algorithm battery_battery algorithm_soc es

- Tracer

- 通过u盘升级stm32固件

- Simple Task Organizer System using JavaScript

- pgcenter:用于观察和排除Postgres故障的命令行管理工具