FPGA实现的线阵CCD驱动时序设计与优化

97 浏览量

更新于2024-09-01

1

收藏 352KB PDF 举报

"基于FPGA的线阵CCD驱动时序电路设计"

本文主要探讨了基于FPGA的线阵CCD(电荷耦合器)驱动时序电路设计,强调了驱动时序在确保CCD芯片性能和稳定输出信号中的关键作用。CCD因其小巧、高精度、低功耗、长寿命和高测量精度等特点,在图像传感和非接触测量领域广泛应用。设计良好的驱动时序能够优化CCD的转换效率和信噪比。

通常,CCD驱动设计有四种方法:EPROM驱动、IC驱动、单片机驱动和PLD(可编程逻辑器件)驱动。其中,FPGA(Field-Programmable Gate Array)作为PLD的一种,因其灵活性和可配置性,常被用于定制CCD驱动时序电路。FPGA可以灵活地实现复杂的时序逻辑,适应不同CCD芯片的需求。

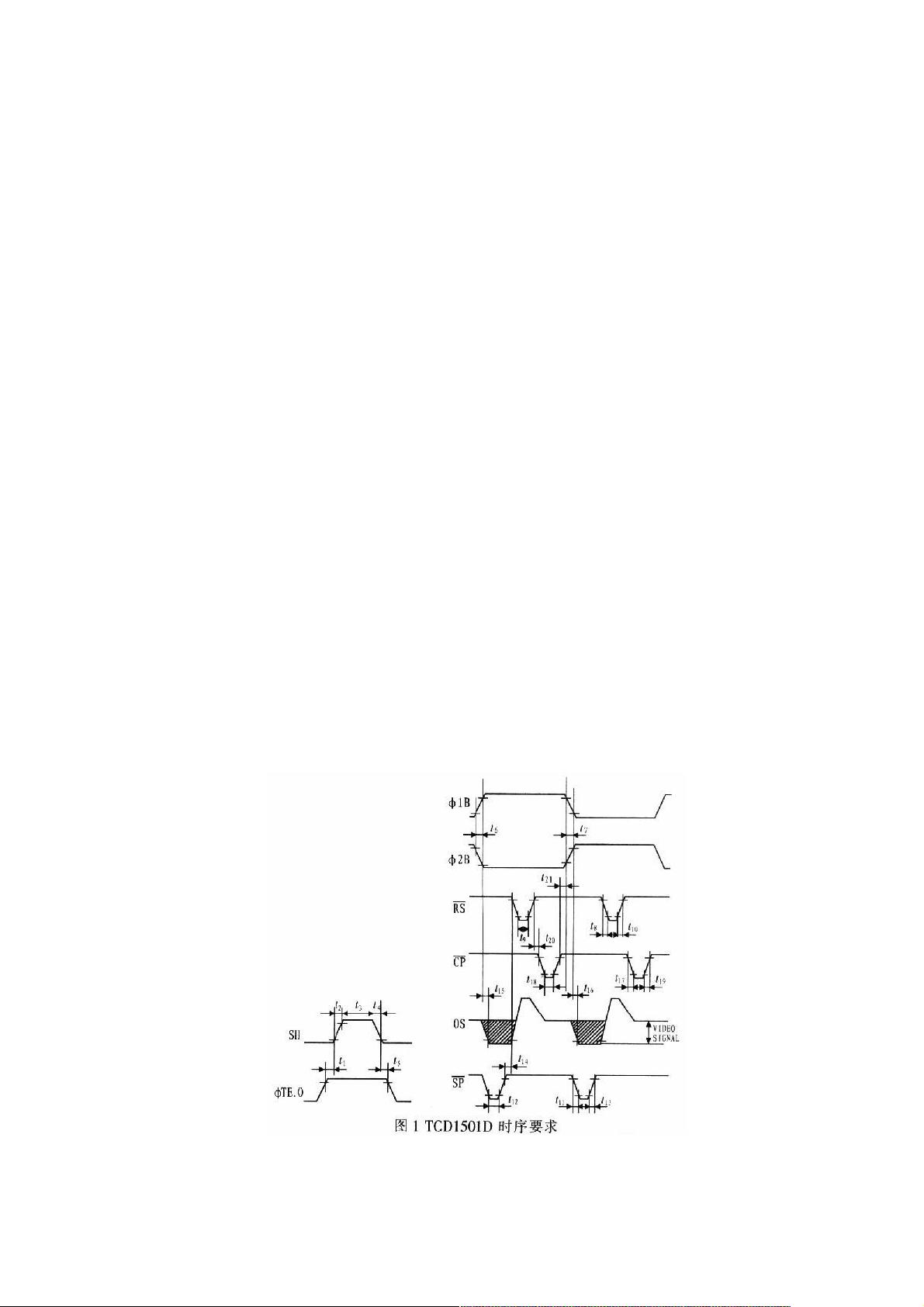

文章详细介绍了TCD1501D这款来自TOSHIBA的线阵CCD,其具有5000个像元,每个像元尺寸为7μm×7μm,光谱响应范围从300nm到1000nm,且动态范围和饱和曝光度都有较高规格。该器件需要特定的驱动脉冲,包括复位时钟RS、移位脉冲φ1、φ2和转移脉冲SH。为了完成一帧图像的传输,需要精确控制这些时钟脉冲的数量和顺序。

在驱动时序分析部分,作者指出正确的时间顺序对CCD的正常运行至关重要,并给出了具体的时序关系图。同时,文中提到了CCD输出信号的采集问题,特别是复位噪声的影响。为减少复位噪声,采用了相关双采样的方法,通过在同一像素周期内两次采样参考电平和信号电平,然后相减来消除噪声。

TCD1501D的一个独特之处在于其内部包含了采样保持电路,可以对视频信号进行采样并钳位,输出一个直流分量,便于后续信号处理。这一内部结构简化了外部电路设计,提高了系统的整体性能。

基于FPGA的线阵CCD驱动时序电路设计是一个涉及硬件设计、信号处理和噪声控制的综合任务。FPGA的使用使得设计更加灵活,能够针对特定的CCD芯片优化驱动方案,以达到最佳的图像质量和系统稳定性。

点击了解资源详情

493 浏览量

531 浏览量

2024-11-03 上传

2024-11-03 上传

243 浏览量

126 浏览量

112 浏览量

181 浏览量

weixin_38631197

- 粉丝: 5

最新资源

- 计算机组成原理期末试题及答案(2011参考)

- 均值漂移算法深入解析及实践应用

- 掌握npm与yarn在React和pg库中的使用

- C++开发学生信息管理系统实现多功能查询

- 深入解析SIMATIC NET OPC服务器与PLC的S7连接技术

- 离心式水泵原理与Matlab仿真教程

- 实现JS星级评论打分与滑动提示效果

- VB.NET图书馆管理系统源码及程序发布

- C#实现程序A监控与自动启动机制

- 构建简易Android拨号功能的应用开发教程

- HTML技术在在线杂志中的应用

- 网页开发中的实用树形菜单插件应用

- 高压水清洗技术在储罐维修中的关键应用

- 流量计校正方法及操作指南

- WinCE系统下SD卡磁盘性能测试工具及代码解析

- ASP.NET学生管理系统的源码与数据库教程