LTE系统中转换预编码的FPGA实现与优化

19 浏览量

更新于2024-09-02

收藏 255KB PDF 举报

"嵌入式系统/ARM技术中的LTE系统中转换预编码的设计及实现"

在现代通信系统中,LTE(长期演进)作为一种高效的数据传输标准,广泛应用于移动通信领域。该技术在上行链路中采用了SC-FDMA(单载波-频分多址)作为传输方案,相比传统的OFDMA(正交频分多址)方法,SC-FDMA具有更低的峰均功率比(PAPR),这对于移动设备尤其重要,因为它能显著提高终端性能,降低功耗,从而延长电池寿命。

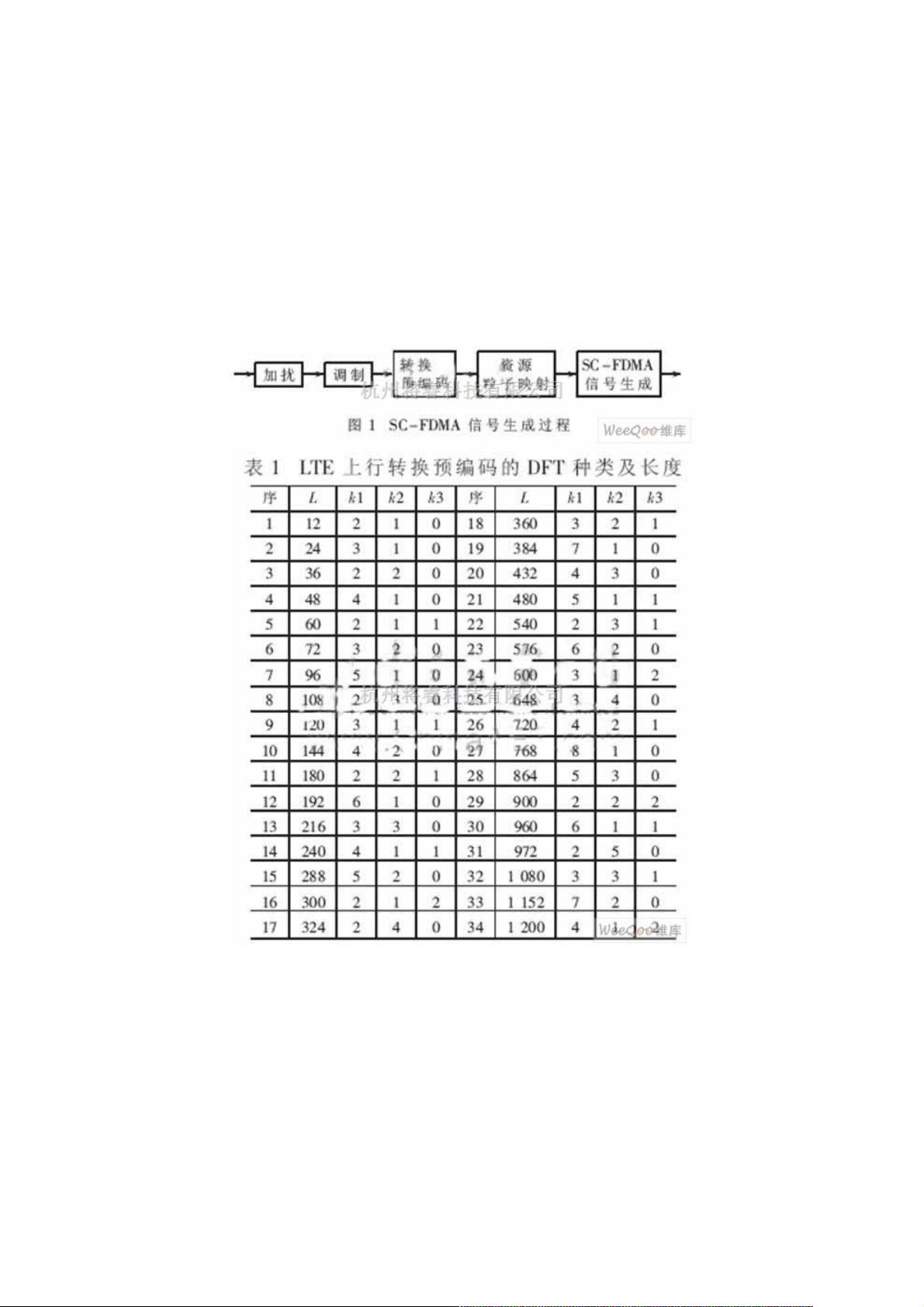

在LTE的物理上行共享信道(PUSCH)的基带信号处理过程中,转换预编码是一个关键步骤。这一过程通常通过离散傅里叶变换(DFT)来实现,如图1所示。这里的DFT采用了一种对称的形式,其变换长度L可以根据需求动态调整,由2的幂、3的幂和5的幂相乘组成,最大不超过1200(L=2k1×3k2×5k3,L≤1200)。由于转换预编码需要处理不同长度的输入,它涉及多种不同类型的DFT,规模较大,这对硬件设计提出了严峻的挑战。

在实现转换预编码时,通常会遇到两种主要的FFT(快速傅里叶变换)算法:Cooley-Tukey算法和Good-Thomas算法。Cooley-Tukey算法因其模块化特性而广受欢迎,支持原位计算,数据和旋转因子的提取有明确的规则。这种算法在基3FFT中也有应用,允许灵活选择因子,所有运算单元相同,简化了实现过程。另一方面,Good-Thomas算法适用于因子互质的情况,由于它省去了中间级的乘法操作,所以计算次数相对较少,但在实现复杂度上稍逊于Cooley-Tukey算法。

在嵌入式系统和ARM技术的背景下,为了应对转换预编码的硬件设计挑战,文章提出了基于FPGA(现场可编程门阵列)的解决方案。FPGA由于其可重配置性和高并行处理能力,成为实现复杂计算任务如DFT的理想平台。通过优化算法和硬件架构,可以在满足性能需求的同时,降低功耗和成本,适应嵌入式系统对体积、功耗和效率的严格要求。

这个研究专注于如何在LTE系统中有效设计和实现转换预编码,特别是在嵌入式环境和ARM处理器上,通过选择合适的FFT算法和利用FPGA的特性,解决大规模DFT计算的难题,以提高通信系统的整体性能。

2020-11-08 上传

2020-10-20 上传

2020-11-08 上传

1738 浏览量

394 浏览量

1131 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38586186

- 粉丝: 9

- 资源: 943

最新资源

- 前端协作项目:发布猜图游戏功能与待修复事项

- Spring框架REST服务开发实践指南

- ALU课设实现基础与高级运算功能

- 深入了解STK:C++音频信号处理综合工具套件

- 华中科技大学电信学院软件无线电实验资料汇总

- CGSN数据解析与集成验证工具集:Python和Shell脚本

- Java实现的远程视频会议系统开发教程

- Change-OEM: 用Java修改Windows OEM信息与Logo

- cmnd:文本到远程API的桥接平台开发

- 解决BIOS刷写错误28:PRR.exe的应用与效果

- 深度学习对抗攻击库:adversarial_robustness_toolbox 1.10.0

- Win7系统CP2102驱动下载与安装指南

- 深入理解Java中的函数式编程技巧

- GY-906 MLX90614ESF传感器模块温度采集应用资料

- Adversarial Robustness Toolbox 1.15.1 工具包安装教程

- GNU Radio的供应商中立SDR开发包:gr-sdr介绍