FPGA新手必看:下载验证问题解析

需积分: 9 42 浏览量

更新于2024-09-11

收藏 638KB PDF 举报

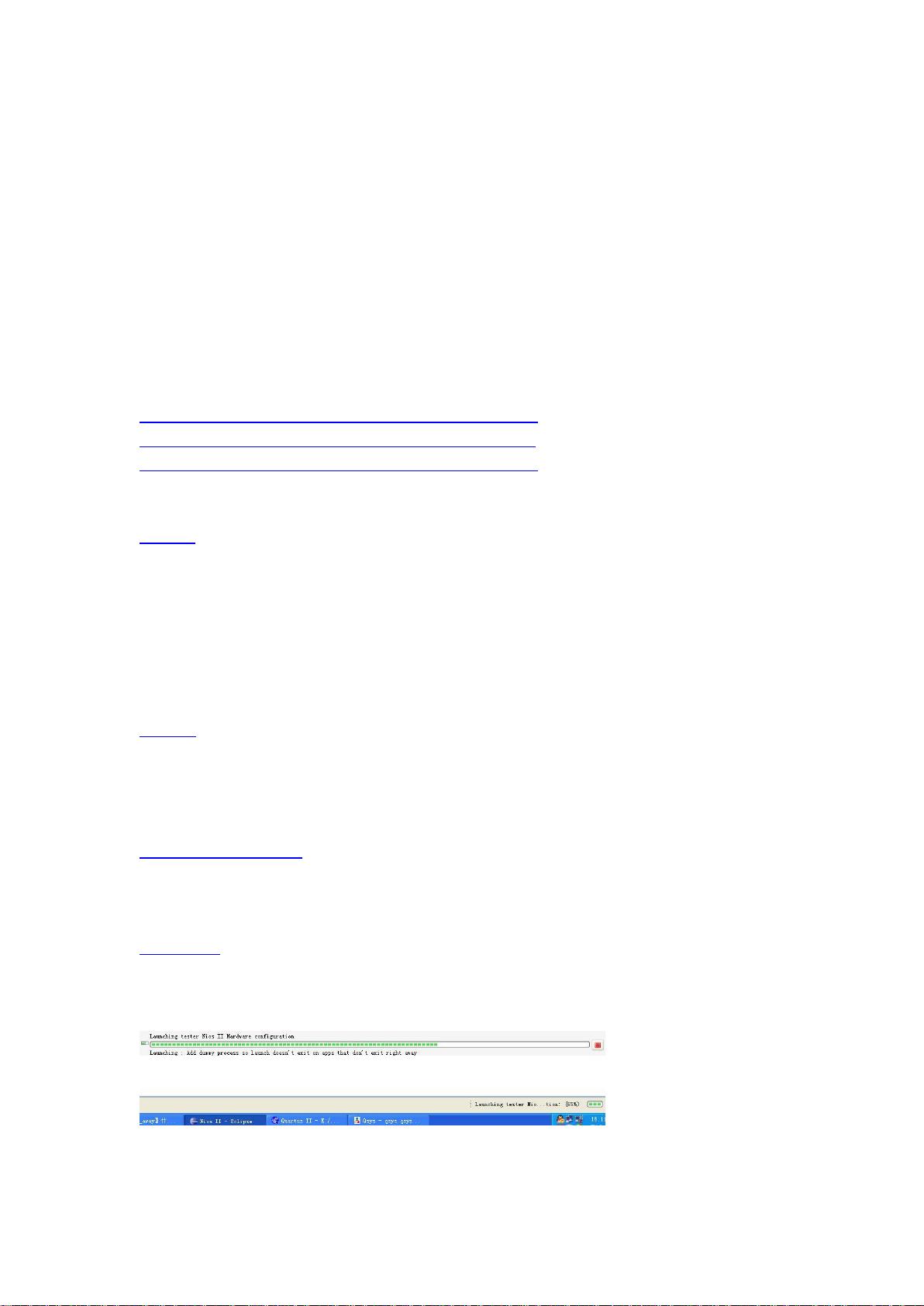

"FPGA经典100问系列教程涵盖了FPGA学习的多个方面,包括HDL语言、仿真、设计实现、下载验证以及入门与提高等主题,旨在帮助初学者全面掌握FPGA技术。FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,用户可以根据需求对其内部逻辑进行配置,广泛应用于各种定制化电子设计中。在学习FPGA的过程中,常见的问题包括硬件描述语言(HDL)的使用、仿真验证、设计实现流程、FPGA的下载与验证等。例如,关于nios2处理器在Cyclone II FPGA上的速度问题,以及在运行时可能出现的卡死现象,都是实际操作中可能遇到的挑战。在没有SDRAM的情况下,程序直接在EPCS4中运行速度会较慢,而FPGA的最大工作频率并不直接等于时钟频率,而是取决于多个因素,如逻辑复杂度、布线延迟等。当遇到nios运行卡死的问题时,可能需要检查调试配置和目标连接以确保正确的通信。"

在FPGA下载验证中,一个重要的知识点是理解FPGA的编程流程,这通常涉及以下步骤:

1. **编写HDL代码**:使用VHDL或Verilog等HDL语言描述逻辑功能。

2. **编译与综合**:将HDL代码转换为门级网表,这个过程包括逻辑优化和资源分配。

3. **布局与布线**:根据综合结果在FPGA内部安排逻辑单元和互连线。

4. **配置文件生成**:将布线后的结果转化为可下载的配置文件,如JTAG或EPCS。

5. **下载验证**:通过JTAG或SPI等接口将配置文件加载到FPGA,然后通过硬件测试来验证设计是否按预期工作。

在处理速度问题时,FPGA的运行速度受多方面因素影响:

- **启动方式**:从ROM直接启动的程序速度通常较慢,因为ROM的访问速度低于RAM。当程序被映射到SDRAM中运行,可以显著提高执行速度。

- **时钟频率**:FPGA的最高工作频率不等于其时钟频率,时钟频率是指内部信号的刷新速率,而运行速度取决于具体实现的逻辑功能。

- **CPU与内存**:CPU与SDRAM之间的交互速度不等于CPU的运行速度,CPU的运行速度是指其执行指令的能力,与内存读写速度、总线带宽等因素有关。

对于硬件调试中的问题,例如nios运行卡死,可能的原因包括:

- **连接问题**:确保硬件连接正确,如JTAG链路、电源、信号完整性等。

- **配置错误**:检查硬件配置文件是否正确匹配目标硬件。

- **软件问题**:确认软件版本兼容性,更新驱动或工具至最新版。

- **调试设置**:在调试模式下检查配置,确保目标连接正确设置。

FPGA的学习不仅需要理解基本原理,还需要实践操作和问题排查能力。通过解答这些问题,初学者可以逐步加深对FPGA的理解,提高解决实际问题的能力。

2019-08-17 上传

2013-06-13 上传

2022-09-23 上传

2022-09-24 上传

2018-05-16 上传

2022-06-26 上传

2021-02-02 上传

点击了解资源详情

yinshuisiquan

- 粉丝: 1

- 资源: 11

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码