Vivado XDC约束详解:提升设计效率的关键

需积分: 33 60 浏览量

更新于2024-09-13

1

收藏 930KB PDF 举报

"XDC约束技巧之时钟篇.pdf"

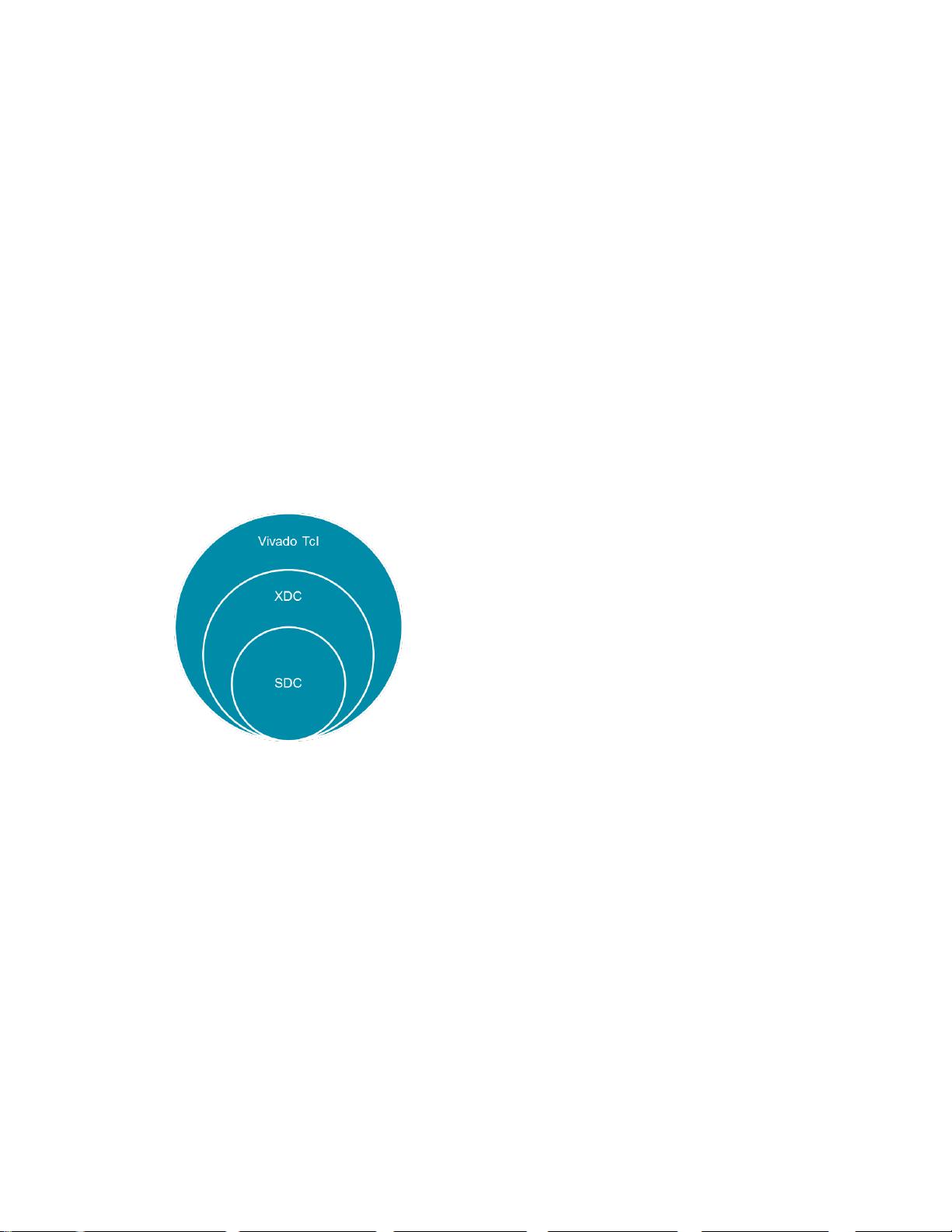

在FPGA设计中,Xilinx的Vivado设计套件引入了XDC(Xilinx Design Constraints)作为新的约束文件格式,相较于旧有的UCF(User Constraint File),XDC在功能和使用上有了显著的提升。XDC基于SDC(Synopsys Design Constraints)标准,而SDC是业界通用的约束规范,因此XDC具备了更好的统一性、可扩展性和高效性。

XDC的优势主要体现在以下几个方面:

1. **统一前后端约束**:XDC使得前端设计和后端实现的约束格式一致,简化了设计流程中的管理。

2. **实时执行**:XDC的命令式特性允许设计者在实现过程中实时录入和执行约束,提高了工作效率。

3. **增量设置**:设计者可以逐步添加和修改约束,加快调试速度。

4. **高覆盖率和可扩展性**:XDC支持更多的设计约束,能更全面地覆盖设计需求。

5. **兼容性与移植性**:由于基于SDC标准,XDC与其他工具和平台有更好的兼容性,方便设计的移植。

XDC与UCF的主要差异在于:

1. **处理方式**:XDC可以作为一个整体文件导入,也可以按命令逐条执行。后输入的约束会覆盖前输入的(时序例外除外),并且在读取时逐条处理,因此约束的顺序非常重要。

2. **时钟假设**:UCF默认所有时钟为异步,而XDC默认所有时钟同步,除非明确指定,这导致XDC在跨时钟域时序分析上更为严格。

XDC的基本语法包含以下三个主要部分:

1. **时钟约束**:定义时钟源,时钟分配,时钟偏移等,这对于确保时序正确性至关重要。例如,`create_clock`命令用于创建一个新的时钟,而`set_clock_groups`用于定义时钟之间的关系(同步或异步)。

2. **I/O约束**:设定输入输出引脚的属性,如速度等级、电压电平、IO标准等。`set_property`命令常用于设置这些属性。

3. **时序例外约束**:在默认同步假设下,设计者可能需要指定某些路径不受同步规则限制,这时就需要使用时序例外约束,如`set_false_path`和`set_max_delay`来排除特定路径的时序检查。

在遵循Xilinx的UltraFast设计方法学时,设计者通常需要按照一定的顺序进行约束,例如先定义时钟,再设置I/O约束,最后处理时序例外,以确保设计的正确性和优化效率。XDC的Tcl基础意味着用户可以利用Tcl的灵活性来编写更复杂或自定义的约束逻辑。

通过理解和熟练掌握XDC,FPGA设计者能够更好地利用Vivado工具,优化设计性能,同时减少设计时间和错误。对于那些对Tcl语言感兴趣的读者,了解和学习Tcl的更多特性将有助于进一步提升在Vivado中的工作效率。

1634 浏览量

773 浏览量

点击了解资源详情

487 浏览量

444 浏览量

422 浏览量

1634 浏览量

131 浏览量

782 浏览量

gegey2008

- 粉丝: 1

最新资源

- C语言实现LED灯控制的源码教程及使用说明

- zxingdemo实现高效条形码扫描技术解析

- Android项目实践:RecyclerView与Grid View的高效布局

- .NET分层架构的优势与实战应用

- Unity中实现百度人脸识别登录教程

- 解决ListView和ViewPager及TabHost的触摸冲突

- 轻松实现ASP购物车功能的源码及数据库下载

- 电脑刷新慢的快速解决方法

- Condor Framework: 构建高性能Node.js GRPC服务的Alpha框架

- 社交媒体图像中的抗议与暴力检测模型实现

- Android Support Library v4 安装与配置教程

- Android中文API合集——中文翻译组出品

- 暗组计算机远程管理软件V1.0 - 远程控制与管理工具

- NVIDIA GPU深度学习环境搭建全攻略

- 丰富的人物行走动画素材库

- 高效汉字拼音转换工具TinyPinYin_v2.0.3发布