基于FPGA的Verilog HDL实现IIC接口设计

需积分: 0 187 浏览量

更新于2024-07-17

1

收藏 1.8MB PDF 举报

"这篇资源是关于基于FPGA的I2C接口设计的研究生课程设计论文,作者使用Verilog HDL语言实现了I2C接口,并在EP2C20Q240C8 FPGA上进行了功能测试。论文涵盖了I2C总线的特点、工作原理、硬件设计、软件代码设计以及模块的实物测试和改进。"

I2C接口设计是嵌入式系统和微控制器通信中的一个重要部分,它由飞利浦公司开发,主要特点是使用两条线——数据线SDA和时钟线SCL,实现设备间的双向串行通信。这种通信协议简单、高效,常用于低速、短距离的数据传输,如连接传感器、显示模块等外围设备。

在I2C总线特点方面,主要有以下几点:

1. **两线制**:只需两条线即可实现多设备通信,降低了硬件成本。

2. **多主控**:总线上可以有多个主控器,每个设备都可以启动和停止通信。

3. **寻址机制**:每个设备都有一个7位或10位的地址,支持多个设备共用同一总线。

4. **主/从模式**:主设备控制时钟,从设备响应主设备的请求。

5. **多种传输速率**:支持标准速(100kbps)、快速速(400kbps)和高速模式(3.4Mbps)。

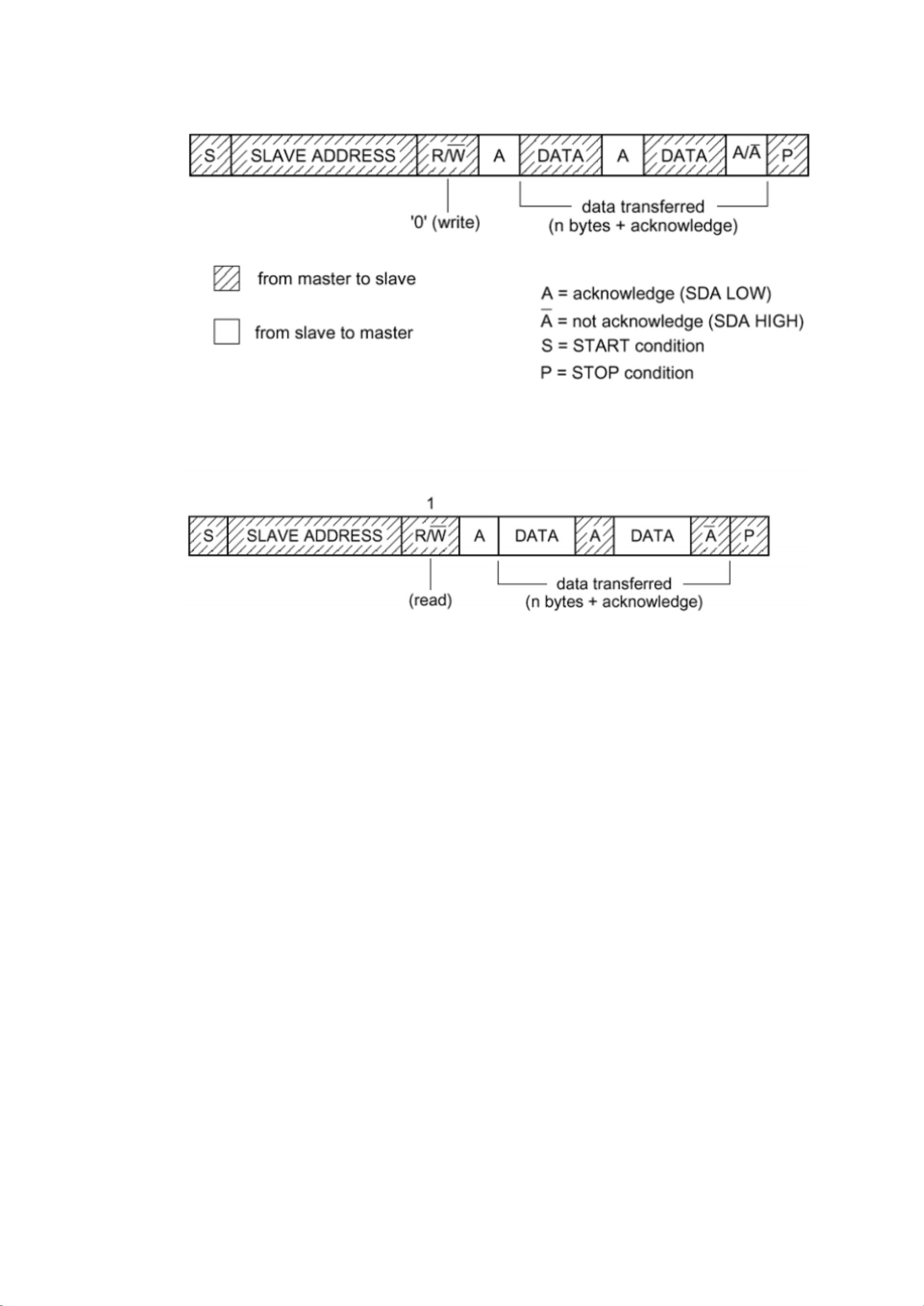

I2C总线的工作原理包括以下几个关键概念:

1. **起始条件**:当SCL为高时,SDA线由高变低,标志着通信的开始。

2. **停止条件**:SCL为高时,SDA线由低变高,表示通信结束。

3. **数据传输**:每个数据位的传输都是在SCL的下降沿进行,SDA线在SCL高电平时保持稳定状态。

4. **应答信号**:每个数据字节传输后,从设备会通过拉低SDA线发送一个应答位,表明已接收数据。

5. **不应答信号**:如果从设备无法接收更多数据或出现错误,会保持SDA线为高电平,表示不应答。

在基于FPGA的I2C接口设计中,通常会包含以下模块:

- **分频模块**:用于生成I2C通信所需的时钟频率,例如100kHz的标准时钟。

- **IIC总线接口模块**:处理I2C协议的具体细节,包括起始/停止条件、数据传输、应答检测等。

- **显示模块**:可能用于调试,将I2C通信的状态和数据可视化显示出来。

- **硬件模块总体设计**:整合各个子模块,形成完整的I2C接口硬件电路。

Verilog HDL代码设计是实现这些模块的关键,通过描述逻辑功能和时序,生成相应的硬件描述语言代码,然后通过EDA工具编译、综合和布局布线,最终在FPGA上实现功能。

在测试阶段,通常会在实际的硬件平台上,如EP2C20Q240C8 FPGA开发板,对I2C接口模块进行功能验证,确保其能正确地发起和接收数据。

论文还提到了IIC接口模块的改进,这可能涉及到提高通信稳定性、增加错误检测和恢复机制、优化代码结构以提高合成效率等方面。

这篇资源提供了对I2C总线的深入理解和基于FPGA实现的实践经验,对于学习和掌握I2C接口设计及Verilog HDL编程具有很高的参考价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

JackLee

- 粉丝: 0

- 资源: 5

最新资源

- 10天学会ASP.NET.pdf

- IBM内部PL1教材中文的

- 107条Javascript的常用语句.txt

- Visual C# 2005微软认证试题

- 一种摄像头自动白平衡的算法及硬件实现

- Linux 的引导过程.pdf

- EXTjs中文手册.pdf

- 你必须知道的.NET.pdf

- JDK5.0新特性介绍.pdf

- sed 使用手册linux unix 下常用的文本处理工具。用来处理格式化文本

- 卷积码的译码算法——维特比译码

- Oracle9i10g编程艺术

- MyEclipse 6 Java EE商业开发中文手册.pdf

- UML参考手册--基本概念

- strust2.0深入浅出

- 计算机专业毕业实习、毕业设计指导书