FPGA设计四大技巧:乒乓操作、串并转换与流水线

下载需积分: 5 | DOCX格式 | 136KB |

更新于2024-09-18

| 186 浏览量 | 举报

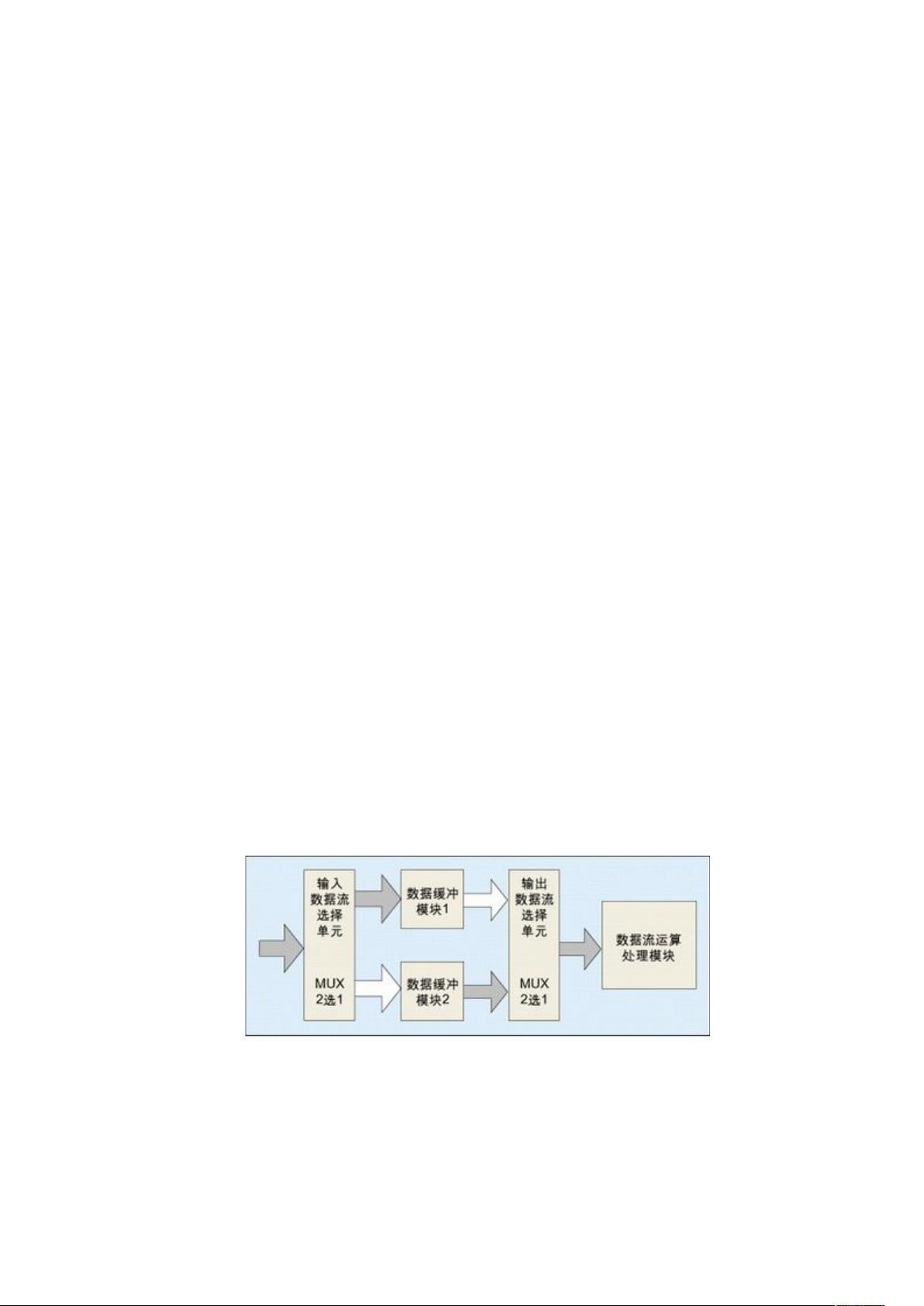

FPGA/CPLD设计中,乒乓操作是一种常用的技术手段,它主要应用于数据流控制,通过灵活切换数据在两个或多个缓冲区之间的传输,实现数据的连续处理而无需停顿。其核心思想是通过“输入数据选择单元”和“输出数据选择单元”的协同工作,将数据流等时分发至不同的缓冲模块(如双口RAM、SPRAM或FIFO),并在缓冲期间进行运算处理。

在一个典型的应用场景中,如WCDMA基带处理,数据流可能包含15个时隙,通过乒乓操作,可以在一个周期内处理两个时隙,节省了单独存储每个时隙所需的缓冲区空间。这种技术特别适用于那些需要进行流水线处理的算法,如数据的预处理、解码、滤波等步骤,能够显著提高处理效率。

乒乓操作的优点还包括:

1. **数据流连续性**:输入和输出数据流看起来是无缝的,没有明显的中断,这有助于优化系统的性能,减少延迟。

2. **硬件资源利用**:通过共享缓冲区,降低了对硬件资源的需求,特别是对于内存空间有限的FPGA/CPLD设计。

3. **可扩展性**:这种设计方法易于扩展,可以增加更多的缓冲区或处理模块,适应不同复杂度的任务需求。

在实际的VHDL设计中,实现乒乓操作的关键在于精确的时序控制和信号逻辑设计,包括数据选择器的状态机设计以及与外部时钟同步的实现。通过适当的寄存器和组合逻辑,可以确保数据在正确的时间被读取和写入缓冲区,从而实现高效的乒乓操作。

此外,除了乒乓操作,文章还提到了其他三种常见的FPGA/CPLD设计思想和技巧,包括串并转换、流水线操作和数据接口同步化。这些技术同样重要,它们能够帮助设计者优化性能、减少设计复杂性和提高资源利用率。例如,串并转换用于高效处理串行数据,流水线操作则通过分解任务并行执行来加快处理速度,而数据接口同步化则确保不同模块间数据的正确传输,防止因时序问题导致的错误。

理解并掌握这些FPGA/CPLD设计思想和技巧,可以帮助工程师在实际项目中更高效地实现电路设计,提升系统的整体性能和可靠性。

相关推荐

sw

- 粉丝: 1

最新资源

- iBATIS 2.0开发指南:入门与高级特性的全面解析

- ESRI Shapefile技术描述详解

- MIF格式详解:GIS地图交换标准

- WEB标准解析与网站重构实践

- 深入解析JUnit设计模式

- PowerDesigner 6.1数据库建模详解与教程

- Spring框架开发者指南(中文版)

- 中文Vim教程:实践导向的手册

- Jboss EJB3.0 实例教程:从入门到精通

- Ant入门与高级应用指南

- Linux系统移植实战:从Bootloader到交叉工具链

- 数缘社区:数学与密码学资源宝库

- ADO.NET深度探索:连接、执行与数据处理

- Eclipse基础入门:集成开发环境详解

- Oracle动态性能视图详解与使用

- Java开发必备:字符串处理与日期转换技巧