5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

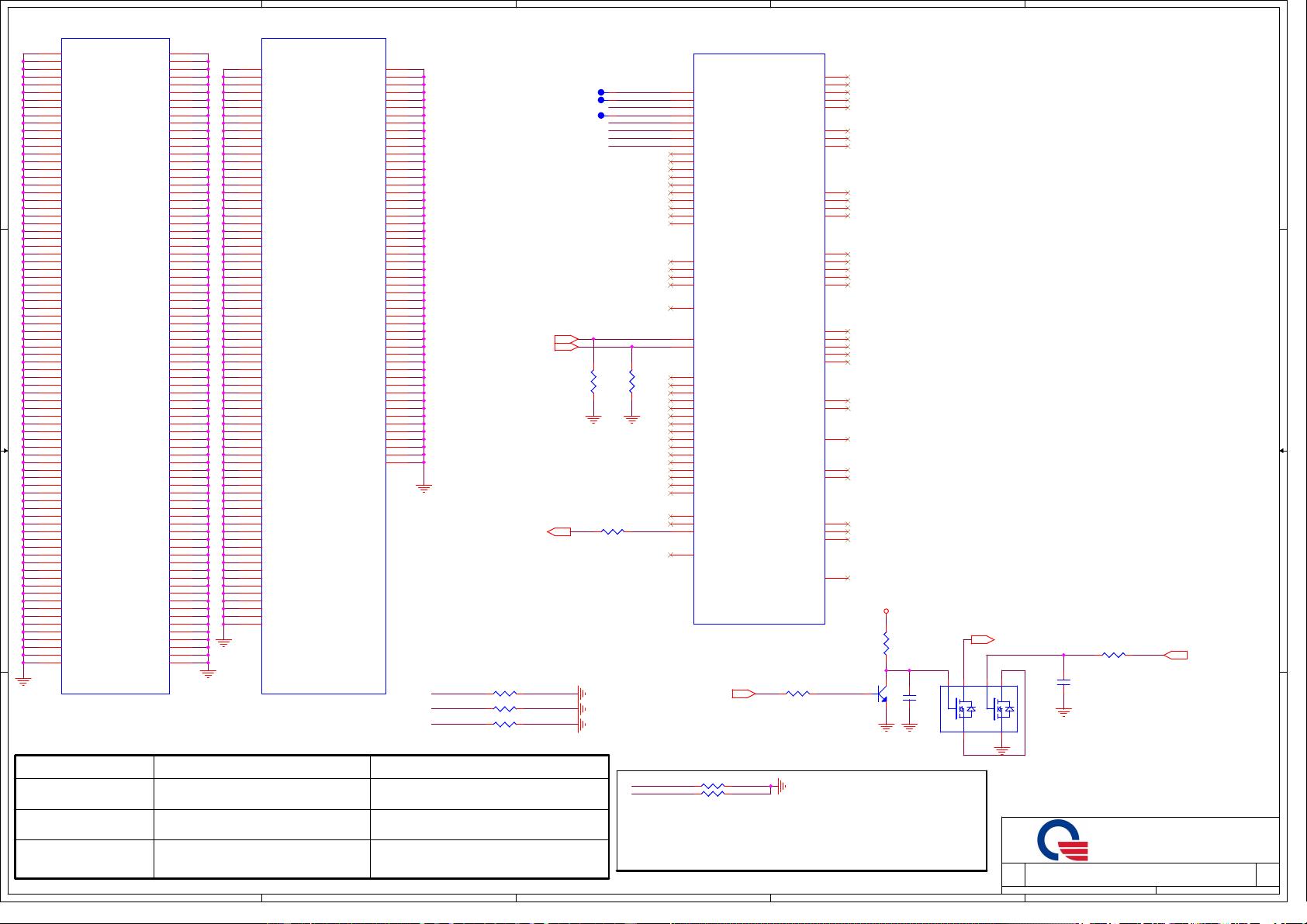

Sandy Bridge Processor (RESERVED, CFG)

CFG4

(DP Presence Strap)

Enable; An ext DP device is connected to eDP

PEG train immediately following

xxRESETB de assertion

CFG2

(PEG Static Lane Reversal)

Processor Strapping

CFG7

(PEG Defer Training)

1 0

Normal Operation

Lane Reversed

Disable; No physical DP attached to eDP

The CFG signals have a default value of '1' if not terminated on the board.

PEG wait for BIOS training

Sandy Bridge Processor (GND)

07

11: (Default) x16 - X16 PEG interface

10: PEG x8 x8 bifurcation enableddisabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG[6:5] (PCIE Port Bifurcation Straps)

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

Sandy Bridge 4/4

1A

Monday, February 21, 2011

Huron River

7 39

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

CFG2

CFG4

CFG7

CFG2

CFG4CFG4

CFG5

CFG6

CFG7CFG7

CFG6

CFG5

H_SNB_IVB#_PWRCTRL(29)

SMDDR_VREF_DQ0_M3(14)

SMDDR_VREF_DQ1_M3(15)

SHDN# (16,19,27,32)

IMVP_PWRGD (8,16,26)

PM_THRMTRIP#(4,11)

+5V

R326

*1K_4

C474

*1000P_4

VSS

U17H

CPU-989P-rPGA

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH26

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

RESERVED

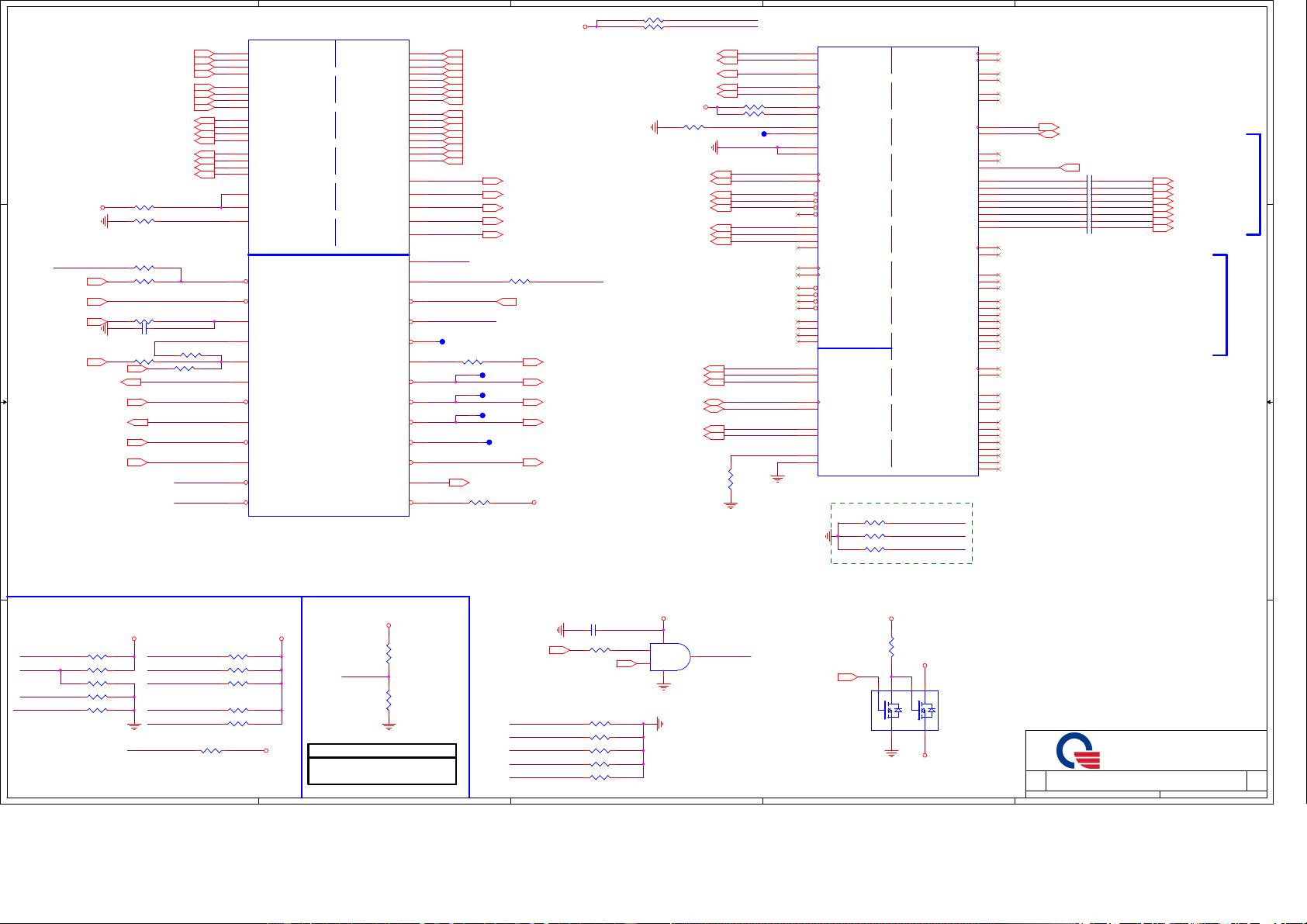

U17E

CPU-989P-rPGA

AK28

AK29

AL26

AL27

AK26

AL29

AL30

AM31

AM32

AM30

AM28

AM26

AN28

AN31

AN26

AM27

AK31

AN29

AM33

AJ27

J16

AT34

H16

G16

AR35

AT33

AR34

AT2

AT1

AR1

B34

A33

A34

B35

C35

AJ32

AK32

AE7

AK2

L7

AG7

J15

C30

D23

A31

B30

D30

B29

A30

B31

C29

J20

T8

B4

D1

F25

F24

D24

G25

G24

E23

W8

AT26

B18

AP35

F23

AJ26

AJ31

AH31

AJ33

AH33

B1

AH27

A19

AN35

AM35

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD34

RSVD35

RSVD38

RSVD42

RSVD39

RSVD40

RSVD41

RSVD43

RSVD45

RSVD56

RSVD57

RSVD58

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD30

RSVD31

RSVD28

RSVD29

RSVD27

RSVD16

RSVD15

RSVD17

RSVD18

RSVD20

RSVD19

RSVD22

RSVD21

RSVD23

RSVD24

RSVD37

RSVD6

RSVD7

RSVD8

RSVD9

RSVD11

RSVD12

RSVD13

RSVD14

RSVD32

RSVD33

RSVD25

RSVD44

RSVD10

RSVD5

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

VCC_VAL_SENSE

VSS_VAL_SENSE

KEY

VCC_DIE_SENSE

VCCIO_SEL

RSVD54

RSVD55

R193 *1K/F_4

R327 *0_4

TP13

R210 1K/F_4

VSS

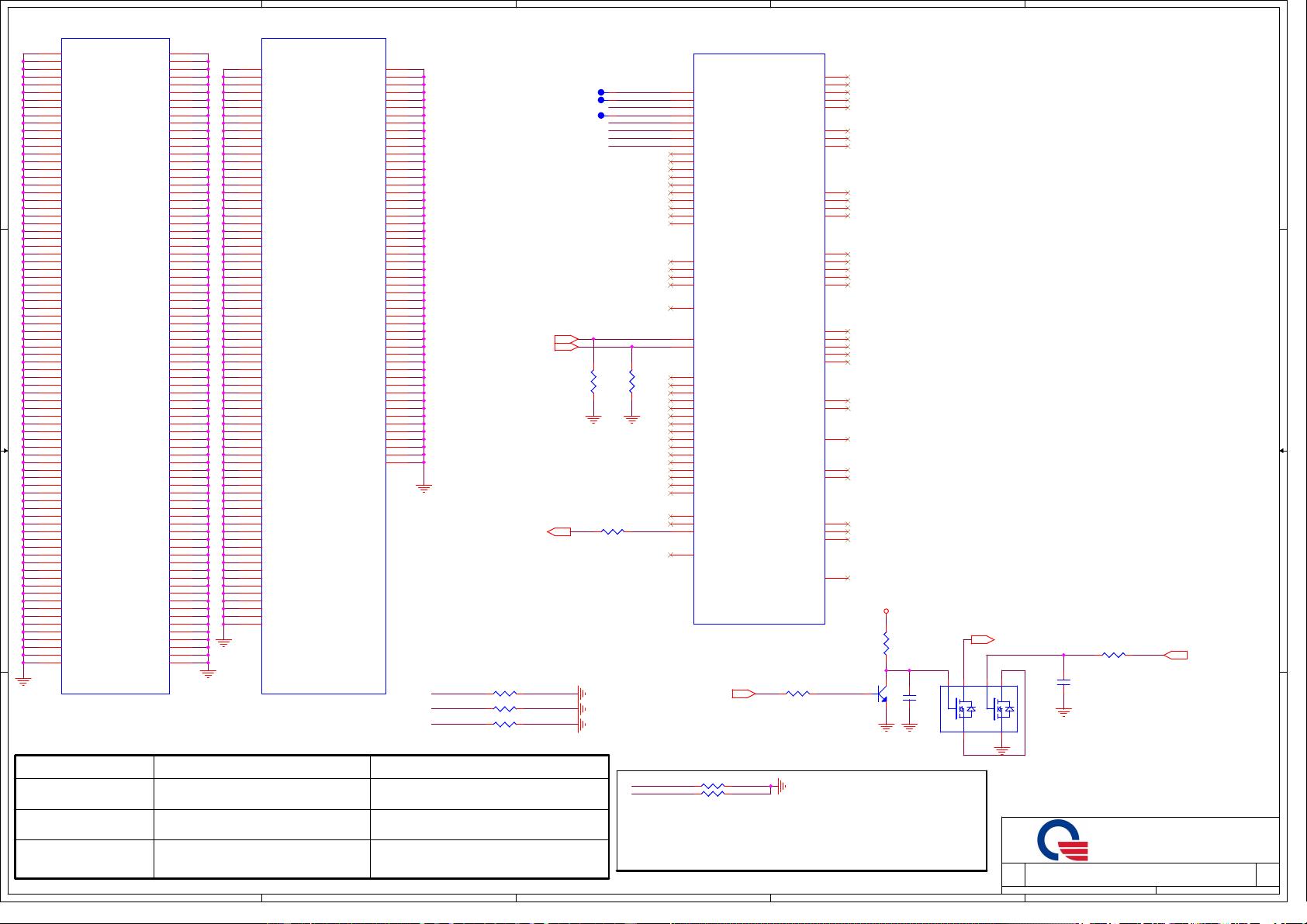

U17I

CPU-989P-rPGA

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

P9

P8

P6

P5

P3

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

M34

L33

L30

L27

L9

L8

L6

L5

L4

L3

L2

L1

K35

K32

K29

K26

J34

J31

H33

H30

H27

H24

H21

H18

H15

H13

H10

H9

H8

H7

H6

H5

H4

H3

H2

H1

G35

G32

G29

G26

G23

G20

G17

G11

F34

F31

F29

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

Q11

2N7002DW

6

2

1

5

4 3

TP12

R209 *1K/F_4

R173

*1K_4

R214

200K/F_4

TP16

Q12

MMBT3904

2

1

3

R212 330/F_4

R196 *1K/F_4

C317

0.1U_4

R366 22/J_4

R194 *1K/F_4