STM32F10X通用定时器中断与寄存器详解

需积分: 1 160 浏览量

更新于2024-08-31

收藏 1.13MB DOCX 举报

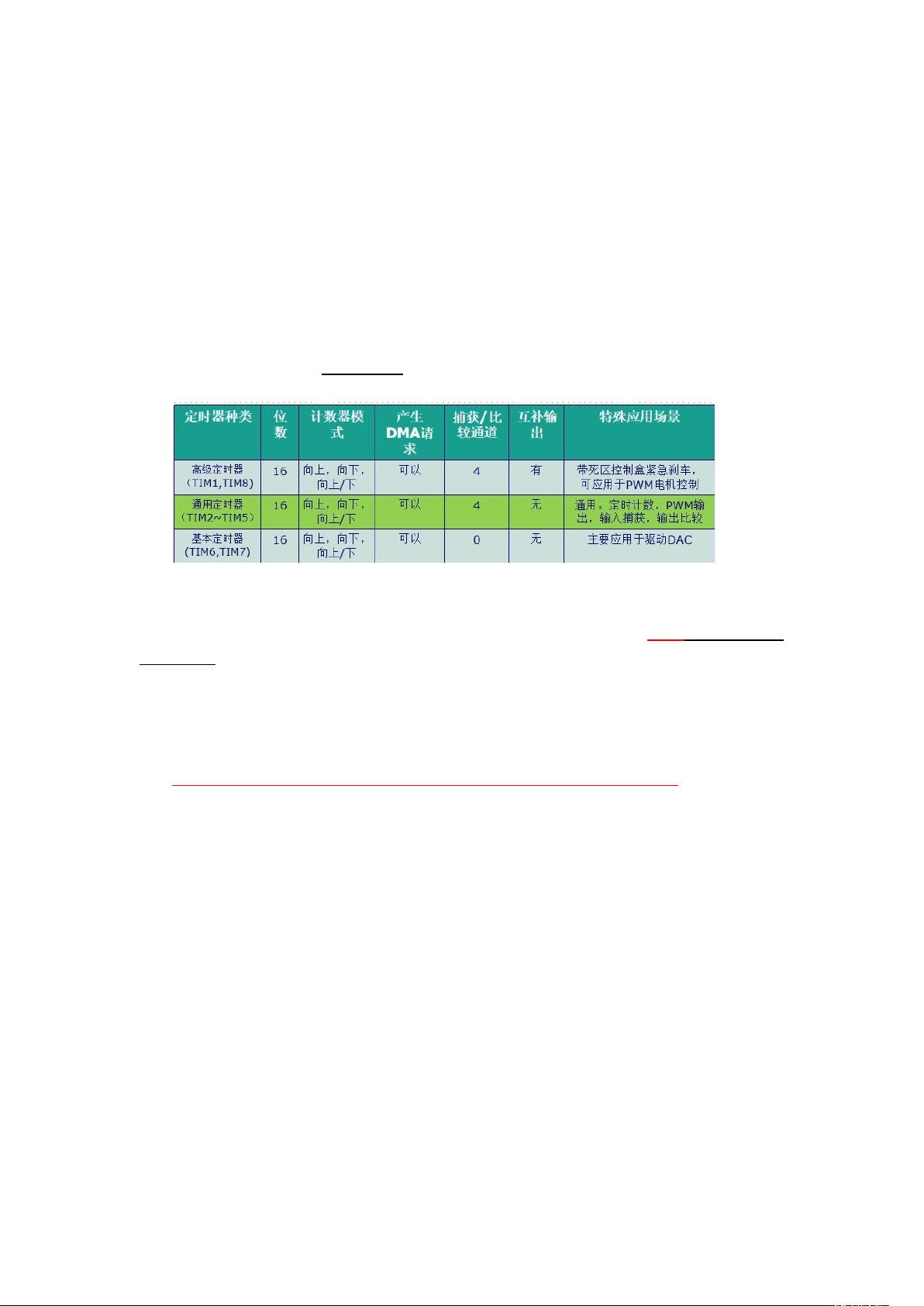

本文档深入解析了STM32F10X系列通用定时器中断的工作原理及其寄存器结构,重点集中在STM32F103型号上。STM32F10X系列拥有8个定时器,其中包括高级定时器TIME1和TIME8,通用定时器TIME2至TIME5,以及基本定时器TIME6和TIME7,每种定时器都有其特定的应用场景。

通用定时器是基于16位自动装载计数器(CNT)和可编程预分频器(PSC),允许精确调整脉冲长度和输出波形周期,范围从几个微秒到几个毫秒。这些定时器具有四个独立通道,支持输入捕获、输出比较、PWM生成和单脉冲模式输出等多种功能。它们能够根据外部信号进行同步,并在特定事件发生时产生中断或DMA请求,如计数溢出、触发事件、输入捕获和输出比较等。

计数器的时钟源非常灵活,可以来自内部时钟(CK_INT)、外部输入脚(TIx)、外部触发输入(ETR)或内部触发输入(ITRx)。内部时钟是最常用的选择,但在某些情况下,可以利用一个定时器作为另一个定时器的预分频器,以实现更复杂的时序控制。

通用定时器中断机制涉及到两个关键部分:时钟源选择和计数部分。时钟源的选择不仅影响计数的精度,还决定了中断触发的条件。通过TIMx_SMCR寄存器,可以设置定时器的行为模式,如是否启用内部时钟,以及是否支持作为其他定时器的预分频器。

本文档旨在帮助读者巩固对STM32F10X系列通用定时器的理解,通过结合“正点原子”教材和STM32中文参考手册,作者提供了实用的教程和详细的操作指南,便于开发者在实际项目中灵活运用和管理这些强大的定时器功能。通过阅读和理解这部分内容,用户可以更好地掌握如何配置定时器、处理中断以及优化其性能,从而提高设计效率和系统的精确性。

244 浏览量

382 浏览量

132 浏览量

154 浏览量

357 浏览量

2021-12-18 上传

2022-07-12 上传

124 浏览量

2022-11-29 上传