DDRSDRAM原理与时序详解:内存提升的秘密

需积分: 50 28 浏览量

更新于2024-07-26

收藏 3.42MB PDF 举报

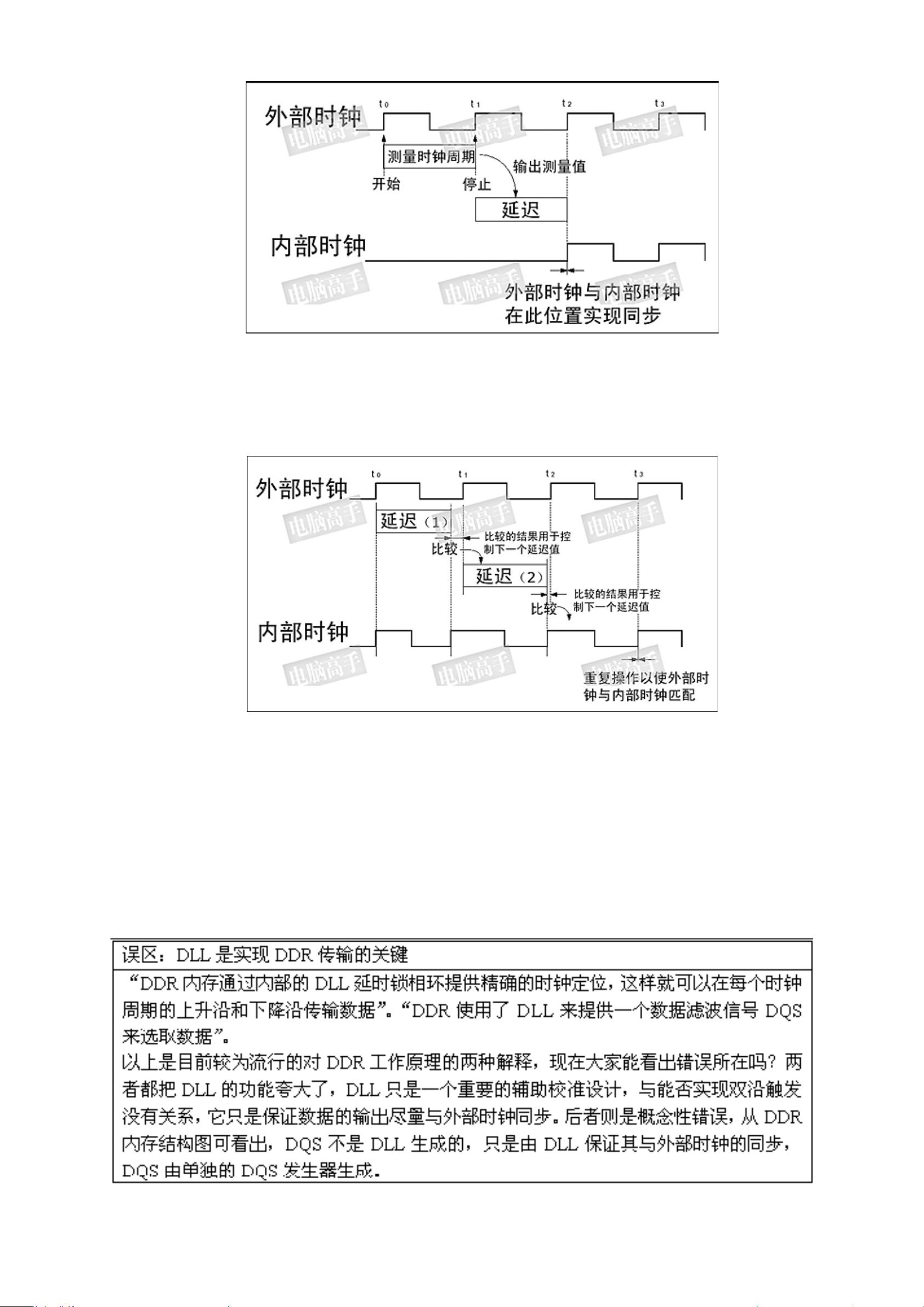

内存的原理和时序-下深入讲解了双倍数据速率同步动态随机访问内存(DDR SDRAM)的工作原理和特点。相比于传统的单倍数据速率SDRAM,DDR SDRAM在设计上有显著改进。它的核心原理在于利用差分时钟信号(CLK#与DQS)实现了在每个时钟周期内两次数据传输,这使得数据传输速率翻倍。

首先,DDR的基本原理涉及到了时钟和数据信号的巧妙配合。在DDRSDRAM的读操作时序图中,CLK#与常规时钟 CLK 相位相反,形成了差分时钟,确保数据在CLK的上升沿和下降沿分别触发,从而达到数据传输的同步。虽然常有文章提及CLK#帮助数据触发,但这只是表层理解,真正的原因在于内存芯片内部的结构优化。

内部结构的变化体现在L-Bank的规格上。在SDRAM中,L-Bank的存储单元容量等于芯片位宽,而在DDR SDRAM中,存储单元容量是一倍于位宽,这意味着地址解码和数据传输的过程有所调整。例如,一个128Mbit的DDR内存,即使位宽与SDRAM相同,其实际的行和列地址寻址能力与SDRAM不同。

读取过程中,DDR SDRAM内部会先将8bit数据一次传送给读取锁存器,然后通过复用器将其拆分为两路4bit数据,并在DQS的控制下在时钟上升和下降沿分别传输。这样的设计使得在100MHz时钟频率下,I/O端口的实际传输速率能达到200MHz,极大地提升了数据传输效率。

DDR SDRAM的出现是基于内存技术的革新,它通过改变时钟信号和内部结构,实现了数据的双倍传输,不仅降低了生产成本,还提升了系统性能,因此在现代计算机系统中占据了主导地位。理解这些原理对于学习和优化内存管理至关重要,特别是对于初学者来说,掌握了DDR SDRAM的内部机制,就能更好地理解和使用这类高速内存。

2019-02-26 上传

2023-10-21 上传

2024-04-12 上传

2023-05-27 上传

2023-09-24 上传

2024-05-21 上传

2023-08-01 上传

hmg727_1

- 粉丝: 0

- 资源: 8

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍