没有合适的资源?快使用搜索试试~ 我知道了~

首页AS3911:高性能NFC启动器/HF读卡器集成电路

"AS3911是一款高性能的NFC启动器/高频读卡器集成电路,适用于基础设施侧的NFC系统,提供优化的射频性能、灵活性和低功耗。该芯片具有独特的自动天线调谐技术,适用于直接驱动天线的应用。"

AS3911技术手册详细介绍了这款集成电路的关键特性与功能。AS3911是一个高度集成的设备,包含了模拟前端(AFE)和一个用于ISO18092(NFCIP-1)启动器、ISO18092主动目标、ISO14443A和B读卡器(包括高速率)以及FeliCa™读卡器的高集成数据帧系统。通过使用AFE并结合外部微控制器实现帧结构,可以实现其他标准和定制协议。

与其他针对移动电话设计的NFC设备相比,AS3911更适合基础设施侧的NFC系统。它提供了最佳的射频性能,同时兼顾了低功耗的需求。该芯片的亮点之一是ams的独特自动天线调谐技术,这使得AS3911在直接驱动天线的应用中表现优异。在HF读卡器IC领域,AS3911独树一帜,因为它包含了两个差分低阻抗(1Ω)的天线驱动器,这有助于提高天线效率和信号质量。

在低功耗应用方面,AS3911包含多个特色功能。它内置了一个低功耗模式,可以在不影响性能的情况下降低功耗,这对于电池供电或能源受限的设备来说至关重要。此外,AS3911还支持智能电源管理,能够根据操作条件动态调整电源配置,进一步节省能量。

除了上述特点,AS3911还提供了强大的安全特性,例如支持AES加密,确保数据传输的安全性。该芯片的接口设计允许与各种微控制器无缝连接,方便开发者进行系统集成。AS3911的多种工作模式(如流模式和透明模式)使其能够适应不同的应用需求,无论是简单的数据交换还是复杂的通信协议,都能轻松应对。

AS3911是一个全面且灵活的NFC解决方案,适合需要高效、低功耗和强大射频性能的基础设施应用,如智能门锁、支付终端、智能标签阅读器等。其独特的特性和功能使得AS3911在NFC技术领域中具有显著的竞争优势。

www.ams.com/3911 Revision 2.3 16 - 96

AS3911

Datasheet - Application Information

8 Application Information

8.1 Operating Modes

The AS3911 operating mode is defined by the content of the

Operation Control Register

.

At power-up all bits of the

Operation Control Register

are set to 0, the AS3911 is in Power-down mode. In this mode AFE static power

consumption is minimized, only the POR and part of the bias are active, the regulators are transparent and are not operating. The SPI is still

functional in this mode so all settings of ISO mode definition and configuration registers can be done.

Control bit

en (bit 7 of the

Operation Control Register

) is controlling the quartz crystal oscillator and regulators. When this bit is set, the

device enters in Ready mode. In this mode the quartz crystal oscillator and regulators are enabled. An interrupt is sent to inform the

microcontroller when the oscillator frequency is stable.

Enable of Receiver and Transmitter are separated so it is possible to operate one without switching on the other (control bits

rx_en and tx_en). In

some cases this may be useful, in case the reader field has to be maintained and there is no transponder response expected receiver can be

switched-off to save current. Another example is NFCIP-1 active communication receive mode in which RF field is generated by the initiator and

only Receiver operates.

Asserting the

Operation Control Register

bit wu while the other bits are set to 0 puts the AS3911 into the Wake-up mode which is used to

perform low power detection of card presence. In this mode the low power RC oscillator and register configurable Wake-up timer are used to

schedule periodic measurement(s). When a difference to the predefined reference is detected an interrupt is sent to wake-up the micro.

Capacitive sensor, phase measurement and amplitude measurement are available.

8.2 Transmitter

The Transmitter contains two identical push-pull driver blocks connected to the pins RFO1 and RFO2. These drivers are differentially driving

external antenna LC tank. It is also possible to operate only one of the two drivers by setting the

IO Configuration Register 1

bit single.

Each driver is composed of 8 segments having binary weighted output resistance. The MSB segment typical ON resistance is 2

Ω, when all

segments are turned on; the output resistance is typically 1

Ω. Usually all segments are turned on to define the normal transmission (non-

modulated) level. It is also possible to switch off certain segments when driving the non-modulated level to reduce the amplitude of signal on the

antenna and/or to reduce the antenna Q factor without making any hardware changes. The

RFO Normal Level Definition Register

defines which segments are turned on to define the normal transmission (non-modulated) level. Default setting is that all segments are turned

on.

Using the single driver mode the number and therefore the cost of the antenna LC tank components is halved, but also the output power is

reduced. In single mode it possible to connect two antenna LC tanks to the two RFO outputs and multiplex between them by controlling the

IO

Configuration Register 1

bit rfo2.

In order to transmit the data the transmitter output level needs to be modulated. The AM and OOK modulation are supported. The type of

modulation is defined by setting the bit

tr_am in the

Auxiliary Definition Register

. For the operation modes supported by the AS3911

framing the setting of modulation type is done automatically by sending direct command

Analog Preset

.

During the OOK modulation (for example ISO14443A) the Transmitter drivers stop driving the carrier frequency; drivers are frozen in state before

the modulation. As consequence the amplitude of the antenna LC tank oscillation decays, the time constant of the decay is defined with the LC

tank Q factor. The decay time in case of OOK modulation can be shortened by asserting the

Auxiliary Definition Register

bit ook_hr. When

this bit is set to logic one the drivers are put in tristate during the OOK modulation.

AM modulation (for example ISO14443B) is done by increasing the output driver impedance during the modulation time. This is done by

reducing the number of driver segments which are turned on. The AM modulated level can be automatically adjusted to the target modulation

depth by defining the target modulation depth in the

AM Modulation Depth Control Register

and sending the

Calibrate Modulation

Depth

direct command. Please refer to the chapter on AM Modulation Depth: Definition and Calibration for further details.

www.ams.com/3911 Revision 2.3 17 - 96

AS3911

Datasheet - Application Information

8.2.1 Slow Transmitter Ramping

When transmitter is enabled it starts to drive the antenna LC tank with full power, the ramping of field emitted by antenna is defined by antenna

LC tank Q factor.

However there are some reader systems where the reader field has to transition with a longer transition time when it is enabled. The STIF

(Syndicat des transports d'Ile de France) specification requires a transition time from 10% to 90% of field longer than or equal to 10µs.

The AS3911 supports that feature. It is realized by collapsing VSP_RF regulated voltage when transmitter is disabled and ramping it when

transmitter is enabled. Typical transition time is 15µs at 3V supply and 20µs at 5V supply.

Procedure to implement the slow transition:

When transmitter is disabled set

IO Configuration Register 2

bit slow_up to 1. Keep this state at least 2ms to allow discharge of

VSP_RF.

Enable transmitter, its output will ramp slowly

Before sending any command set the bit slow_up back to 0.

8.3 Receiver

The receiver performs demodulation of the transponder sub-carrier modulation which is superimposed on the 13.56 MHz carrier frequency. It

performs AM and/or PM demodulation, amplification, band-pass filtering and digitalization of sub-carrier signals. Additionally it performs RSSI

measurement, automatic gain control (AGC) and Squelch function.

In typical application the Receiver inputs RFI1 and RFI2 are outputs of capacitor dividers connected directly to the terminals of antenna coil.

Such concept assures that the two input signals are in phase to the voltage on antenna coil. Care has to be taken during design of capacitive

divider that the RFI1 and RFI2 input signal pp value does not exceed the VSP_A supply voltage.

Receiver comprises two complete receive channels for AM demodulation and PM demodulation. In case both channels are active the selection

of channel used for reception framing is done automatically by receive framing logic. The receiver is switched on when

Operation Control

Register

bit rx_en is set to one. Additionally the

Operation Control Register

contains bits rx_chn and rx_man, rx_chn defines whether

both, AM and PM, demodulation channels will be active or only one of them, while bit

rx_man defines the channel selection mode in case both

channels are active (automatic or manual). Operation of the Receiver is controlled by four Receiver Configuration registers.

The operation of the receiver is additionally controlled by the signal

rx_on which is set high when modulated signal is expected on the receiver

input. This signal is used to control RSSI and AGC and also enables processing of receiver output by Framing logic. Signal

rx_on is

automatically set high after Mask Receive timer expires. Signal

rx_on can also be directly controlled by the controller by sending direct

commands

Mask Receive Data

and

Unmask Receive Data

. Figure 5 illustrates the Receiver block diagram.

8.3.1 Demodulation Stage

First stage performs demodulation of transponder sub-carrier response signal, which is superimposed on HF field carrier. Two different blocks

are implemented for AM demodulation: Peak Detector and AM demodulator mixer. The choice of the demodulator, which is used, is made by the

Receiver Configuration Register 1

bit amd_sel.

Peak detector performs AM demodulation using peak follower. Both, the positive and negative peaks are tracked to suppress common mode

signal. It is limited in speed; it can operate for sub-carrier frequencies up to fc/8 (1700kHz). It has demodulation gain G = 0.7. Its input is taken

from one demodulator input only (usually RFI1).

AM demodulator mixer uses synchronous rectification of both receiver inputs (RFI1 and RFI2). Its gain is G = 0.55. Mixer demodulator is

optimized for VHBR sub-carrier frequencies. (fc/8 and higher). For sub-carrier frequency fc/8 (1700kHz) both peak follower and mixer can be

used, while for fc/4 and fc/2 are supported only by mixer.

By default the Peak detector is used, for data rates fc/8 and higher use of mixer is automatically preset by sending direct command

Analog

Preset

.

PM demodulation is also done by a mixer. The PM demodulator mixer has differential outputs with 60mV differential signal for 1% phase change

(16.67mV per degree). Its operation is optimized for sub-carrier frequencies up to fc/8 (1700 kHz).

In case the demodulation is done externally of the AS3911 it is possible to multiplex the LF signals applied to pins RFI1 and RFI2 directly to the

gain and filtering stage by selecting the

Receiver Configuration Register 2

bit lf_en.

www.ams.com/3911 Revision 2.3 18 - 96

AS3911

Datasheet - Application Information

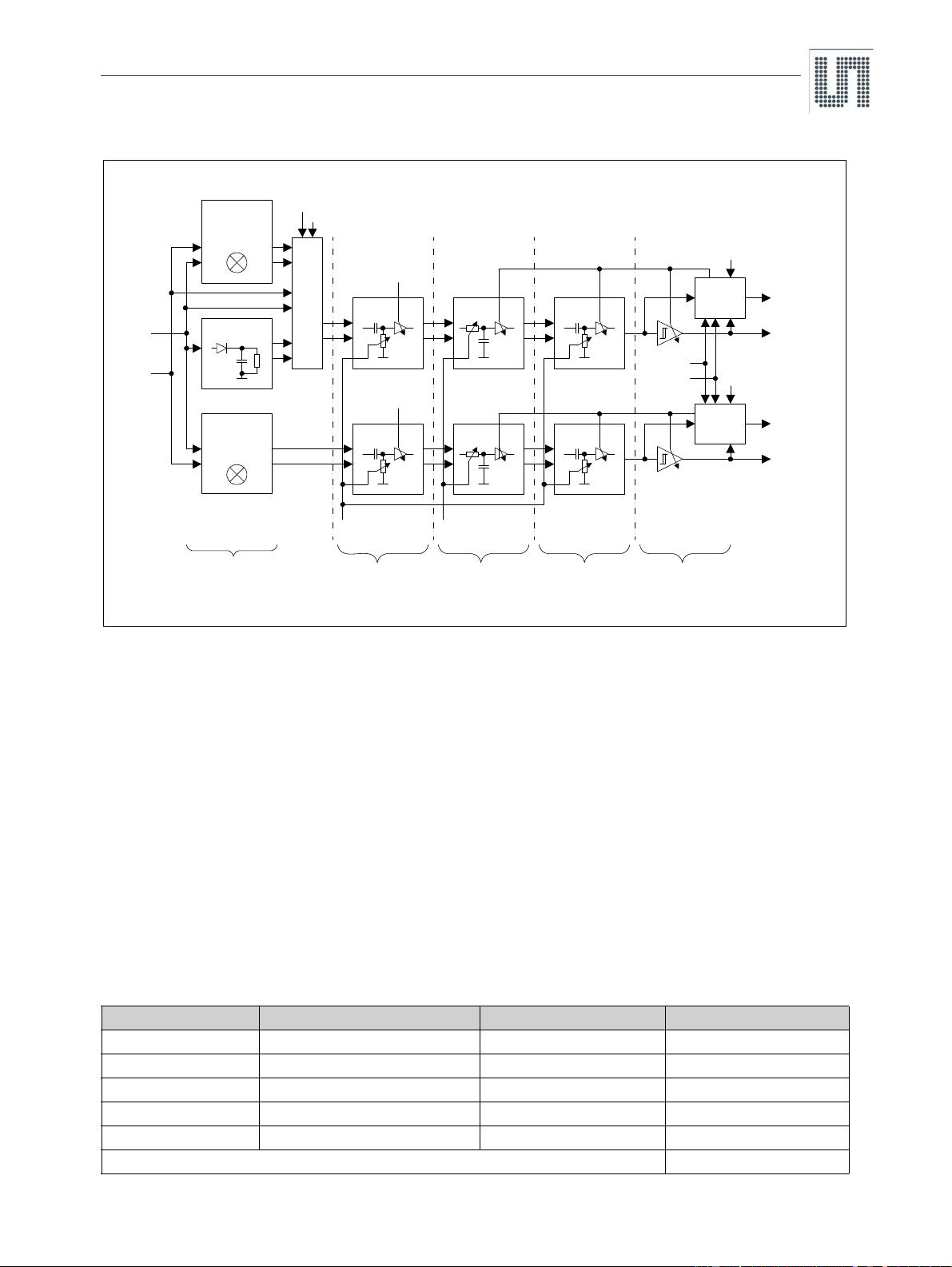

Figure 5. Receiver Block Diagram

8.3.2 Filtering and Gain Stages

The receiver chain has band pass filtering characteristics. Filtering is optimized to pass sub-carrier frequencies while rejecting carrier frequency

and low frequency noise and DC component. Filtering and gain is implemented in three stages where the first and the last stage have the first

order high pass characteristics, while the mid stage has second order low pass characteristic.

Gain and filtering characteristics can be optimized for current application by writing the

Receiver Configuration Register 1

(filtering),

Receiver Configuration Register 3

(gain in first stage) and

Receiver Configuration Register 4

(gain in second and third stage).

Gain of first stage is about 20dB and can be reduced in six 2.5dB steps. There is also a special boost mode available, which boosts the

maximum gain for additional 5.5 dB. In case of VHBR (fc/8 and fc/4) the gain is lower. The first stage gain can only be modified by writing

Receiver Configuration Register 3

. The default setting of this register is the minimum gain. Default first stage zero is located at 60 kHz, it

can also be lowered to 40kHz or 12kHz by writing option bits in the

Receiver Configuration Register 1

. The control of the first and third

stage zeros is done with common control bits (see Table 8)

Gain in the second and third stage is 23dB and can be reduced in six 3dB steps. Gain of these two stages is included in AGC and Squelch loops

or can be manually set in

Receiver Configuration Register 4

. Sending of direct command

Reset Rx Gain

is necessary to initialize the

AGC, Squelch and RSSI block. Sending this command clears the current Squelch setting and loads the manual gain reduction from

Receiver

Configuration Register 4

. Second stage has a second order low pass filtering characteristic, the pass band is adjusted according to sub-

carrier frequency using the bits lp2 to lp0 of the

Receiver Configuration Register 1

. See Table 7 for -1dB cut-off frequency for different

settings.

Table 7. Low Pass Control

rec1<5> lp2 rec1<4> lp1 rec1<3> lp0 -1 dB point

0 0 0 1200 kHz

0 0 1 600 kHz

0 1 0 300 kHz

10 02 MHz

10 17 MHz

Other Not used

digital

sub-carrier

AM

Demodulator

Mixer

Peak Detector

AGC

Squelch

RSSI

rec4<7:4>

AGC

Squelch

RSSI

rec4<3:0>

rec3<7:5>

rec3<4:2>

rec3<2:0> rec1<5:3>

digital

sub-carrier

AC coupling

+ 1

st

gain stage

Low-pass

+ 2

nd

gain stage

High-pass

+ 3

rd

gain stage

Digitizing

stage

Demodulation

stage

M

U

X

PM

Demodulator

Mixer

rec1<7:6>

rec2<6:5>

RF_IN1

RF_IN2

RSSI_AM<3:0>

RSSI_PM<3:0>

RX_on

sg_on

www.ams.com/3911 Revision 2.3 19 - 96

AS3911

Datasheet - Application Information

Table 9 provides information on the recommended filter settings. For all supported operation modes and receive bit rates there is an automatic

preset defined, additionally some alternatives are listed. Automatic preset is done by sending direct command

Analog Preset

. There is no

automatic preset for Steam and Transparent modes. Since selection of filter characteristics also modifies gain, the gain range for different filter

settings is also listed.

8.3.3 Digitizing Stage

Digitizing stage is producing a digital form of sub-carrier signal which is output of Receiver and input to Framing Logic. It is a window comparator

with adjustable digitizing window (five possible settings, 3dB steps, adjustment range from ±33mV to ±120mV). Adjustment of the digitizing

window is included in AGC and Squelch loops or can be manually set in

Receiver Configuration Register 4

.

8.3.4 AGC, Squelch and RSSI

As mentioned above second and third gain stage gain and the Digitizing stage digitizing window are included in AGC and Squelch loops. Eleven

settings are available, default state features minimum digitizer window and maximum gain, first four steps increase the digitizer window in 3dB

steps, next six steps additionally reduce the gain in 2

nd

and 3

rd

gain stage also in 3dB steps. The initial setting with which Squelch and AGC start

is defined in

Receiver Configuration Register 4

. The

Gain Reduction State Register

displays the actual state of gain which results

from Squelch, AGC and initial settings in

Receiver Configuration Register 4

.

Table 8. First and Third Stage Zero Setting

rec1<2> h200 rec1<1> h80 rec1<0> z12k First Stage Zero Third Stage Zero

0 0 0 60 kHz 400 kHz

1 0 0 60 kHz 200 kHz

0 1 0 40 kHz 80 kHz

0 0 1 12 kHz 200 kHz

0 1 1 12 kHz 80 kHz

1 0 1 12 kHz 200 kHz

Other Not used

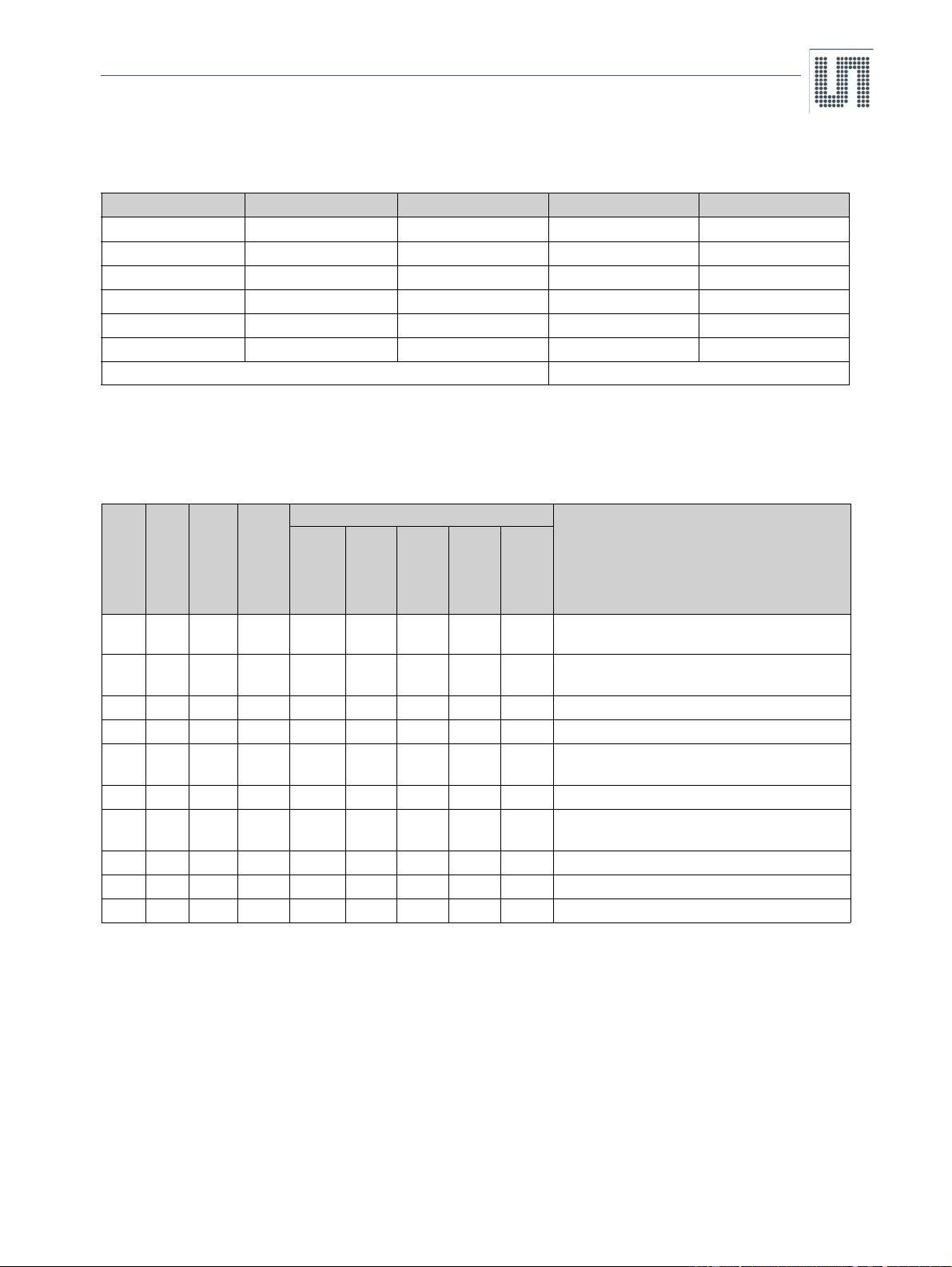

Table 9. Receiver Filter Selection and Gain Range

rec1<5:3>

lp<2:0>

rec1<2>

h200

rec1<1>

h80

rec1<0>

z12k

Gain [dB]

Comment

Max All

Min1 Max23

Max1 Min23

Min All

With Boost

000 0 0 0 43.4 28 26.4 11 49.8

Automatic preset for ISO14443A fc/128 and NFC

Forum Type 1 Tag

000 1 0 0 44 29 27.5 12 49.7

Automatic preset for ISO14443B fc/128

ISO14443 fc/64

001 1 0 0 44.3 29 27 11.7 49.8

Recommended for 424/484 kHz sub-carrier

000 0 1 0 41.1 25.8 23.6 8.3 46.8

Alternative choice for ISO14443 fc/32 and fc/16

100 0 1 0 32 17 17.2 2 37.6

Automatic preset for ISO14443 fc/32 and fc/16

Alternative choice for fc/8 (1.7 kb/s)

100 0 0 0 32 17 17.2 2 37.6

Alternative choice for fc/8 (1.7 kb/s)

000 0 1 1 41.1 25.8 23.6 8.3 46.8

Automatic preset FeliCa (fc/64, fc/32)

Alternative choice for ISO14443 fc/32 and fc/16

101 0 1 0 30 20 12 2 34

Alternative choice for fc/8 and fc/4

101 1 0 0 30 20 12 2 34

Automatic preset for fc/8 and fc/4

000 1 0 1 36.5 21.5 24.9 9.9 41.5

Automatic preset for NFCIP-1 (initiator and target)

www.ams.com/3911 Revision 2.3 20 - 96

AS3911

Datasheet - Application Information

Squelch. This feature is designed for operation of receiver in noisy environment. The noise can come from tags in which processing of data

sent by the reader is going on and an answer is being prepared. Noise can also be generated by noisy environment. This noise may be

misinterpreted as start of transponder response which results in decoding error.

During execution of the Squelch procedure the output of Digitizing comparator is observed. In case there are more than two transitions on this

output in 50µs time period, gain is reduced for 3dB and output is observed during next 50µs. This procedure is repeated until number of

transitions in 50µs is lower or equal to 2 or until maximum gain reduction is reached. This setting is cleared by sending direct command

Reset

Rx Gain

.

There are two possibilities of performing squelch: automatic mode and using direct command

Squelch

.

Automatic mode is started in case bit sqm_dyn in the

Receiver Configuration Register 2

is set. It is activated automatically 18.88µs

after end of Tx and is terminated with Mask Receive timer expire. This mode is primarily intended to suppress noise generated by tag

processing during the time when the tag response is not expected (covered by Mask Receive timer).

Command

Squelch

is accepted in case it is sent when signal rx_on is low. It can be used in case the time window in which noise is present

is known by the controller.

AGC. AGC (automatic gain control) is used to reduce gain to keep receiver chain out of saturation. In case gain is properly adjusted the

demodulation process is also less influenced by system noise.

AGC action starts when signal

rx_on is asserted high and is reset when it is reset to low. At low to high transitions of the rx_on the state of the

receiver gain is stored in the

Gain Reduction State Register

, therefore reading this register later gives the information of the gain setting

used during last reception.

When AGC is switched on receiver gain is reduced so that the input to digitizer stage is not saturated. The AGC system comprises a window

comparator which has its window 3.5 times larger than window of digitalization window comparator. When the AGC function is enabled gain is

reduced until there are no transitions on its output. Such procedure assures that the input to digitalization window comparator is less than 3.5

times larger than its window.

AGC operation is controlled by the control bits

agc_en, agc_m and agc_fast in the

Receiver Configuration Register 2

. Bit agc_en enables

the AGC operation; bit

agc_m defines the AGC mode while bit agc_alg define the AGC algorithm.

Two AGC modes are available, AGC can operate during complete Rx process (as long as signal

rx_on is high) or it can be enabled only during

first eight sub-carrier pulses.

Two AGC algorithms are available; AGC can either start by presetting of code 4h (max digitizer window, max gain) or by resetting the code to 0h

(min digitizer window, max gain). Algorithm with preset code is faster, therefore it is recommended for protocols with short SOF (like ISO14443A

fc/128).

Default AGC settings are: AGC is enabled, AGC operates during complete Rx process, algorithm with preset is used.

RSSI. The receiver also performs the RSSI (Received Signal Strength Indicator) measurement of both channels. RSSI measurement is started

after rising edge of

rx_on. It stays active while signal rx_on is high; while rx_on is low it is frozen. It is a peak hold system; the value can only

increase from initial zero value. Every time the AGC reduces the gain the RSSI measurement is reset and starts from zero. Result of RSSI

measurements is 4-bit value which can be observed by reading the

RSSI Display Register

. The LSB step is 2.8dB, the maximum code is Dh

(13d).

Since the RSSI measurement is of peak hold type the RSSI measurement result does not follow any variations in the signal strength (the highest

value will be kept). In order to follow RSSI variation it is possible to reset RSSI bits and restart the measurement by sending direct command

Clear RSSI

.

8.3.5 Receiver in NFCIP-1 Active Communication Mode

There are several features built in receiver to enable reliable reception of active NFCIP-1 communication. All these settings are automatically

preset by sending direct command

Analog Preset

after the NFCIP-1 mode has been configured. In addition to filtering options there are two

NFC specific configuration bits stored in the

Receiver Configuration Register 3

.

Bit

lim enables clipping circuits which are positioned after first and second gain stages. The intention of clipping circuits is to limit the signal level

for the following filtering stage (in case the NFC peer is close the input signal level can be quite high).

Bit

rg_nfc forces gain reduction of second and third filtering stage to -6dB while keeping the digitizer comparator window at maximum level.

剩余95页未读,继续阅读

2013-12-26 上传

2021-09-29 上传

2024-10-17 上传

2020-06-29 上传

2019-10-22 上传

2021-05-19 上传

信息安全专家

- 粉丝: 82

- 资源: 13

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功