DDR2 SDRAM操作时序详解与FPGA控制策略

需积分: 50 79 浏览量

更新于2024-07-27

1

收藏 2.54MB PDF 举报

DDR2 SDRAM是一种先进的动态随机访问存储器技术,其操作时序规范对于FPGA(现场可编程门阵列)处理这种内存至关重要。在进行FPGA与DDR2 SDRAM的交互时,理解其工作原理和控制信号是至关重要的。

首先,DDR2 SDRAM的基本功能包括突发模式的数据传输。它采用突发读写模式,用户需要指定一个簇(由BA0和BA1选择)和行(由A0-A13确定),并根据预先设置的突发长度(通常是4或8个地址)进行连续的数据交换。每次访问前,必须先通过激活命令启动操作,随后跟随读或写命令。同时,地址线会携带突发读写的起始列地址和是否执行自动预充电的控制信息。

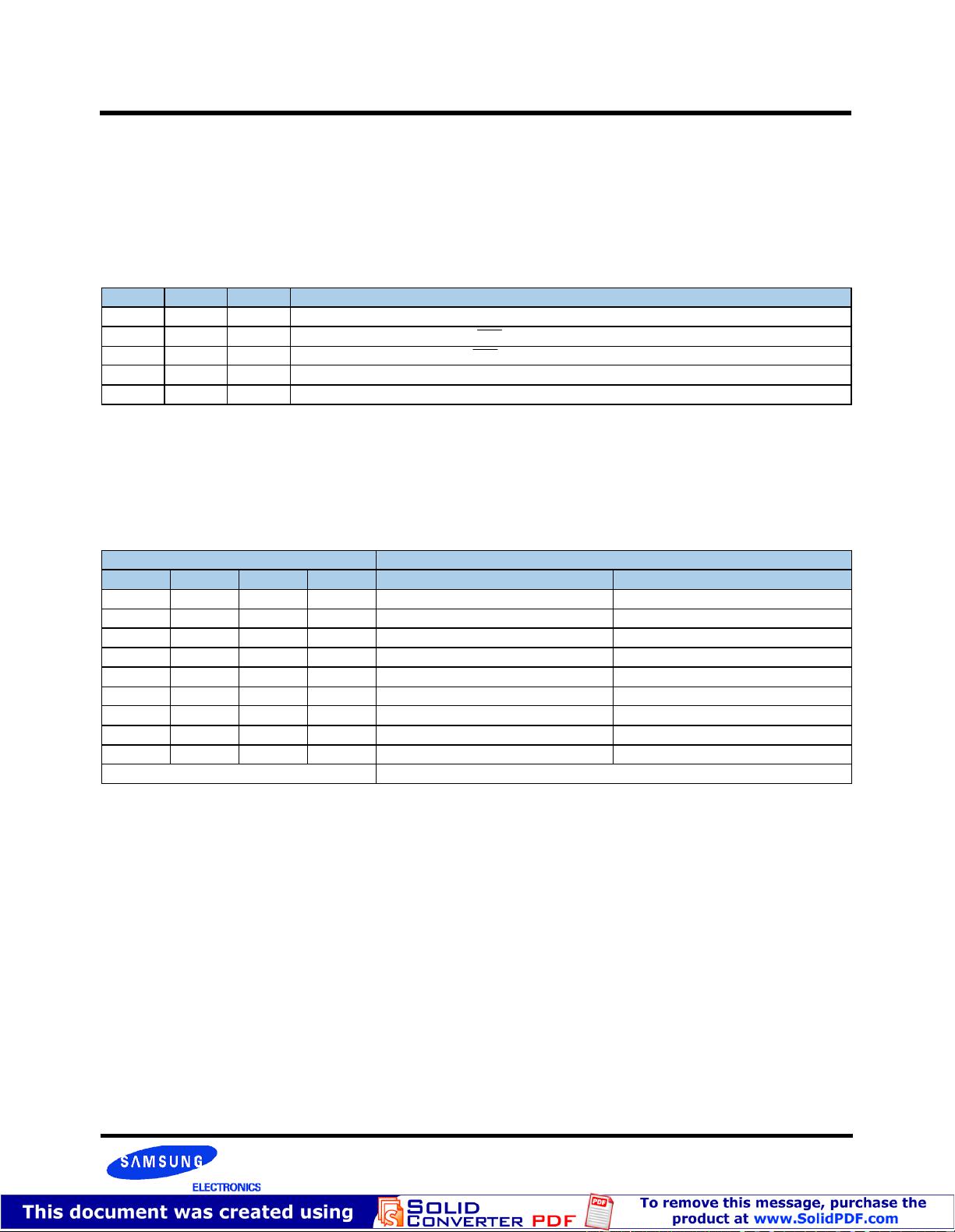

初始化是使用DDR2 SDRAM的第一步,它涉及设置寄存器、配置参数以及确保设备按照特定时序进入工作状态。上电和初始化过程需遵循严格的时序规定:

1. 在上电时,首先确保CKE(时钟信号)低于0.2倍的VDDQ电压(电源电压),这是为了防止过快的电压变化对内存造成损害。然后,逐步增加电源到正常工作电压,同时保持CKE处于低电平状态,等待特定的时序延迟。

2. 接下来,执行CKEL(时钟边缘低电平)命令,进入断电状态,此时内存单元停止接收新的数据。在这个状态下,可以进行校准操作,如自我刷新(SRF)以恢复部分存储单元的性能。

3. 当完成校准后,通过设定模式寄存器(MRS和(E)MRS)来配置内存模式和操作参数。自我刷新结束后,CKEH上升,标志着断电状态结束,内存设备重新准备接收数据。

4. 激活命令(ACT)用于唤醒一个簇,允许后续的读写操作。写入数据(Write)和读取数据(Read)命令会根据需要发送,包括带有自动预充电的WRA和RDA,以及PR(预充电)命令来预先为即将使用的行供电。

5. 在某些情况下,可能需要使用额外的控制命令,如预充电所有簇(PR(A))、设定模式寄存器(EMRS)等,以实现更精细的内存管理。

6. 写入或读取操作完成后,内存可能会进入空闲状态,此时内存单元已经准备好接受新的命令,但没有正在进行的数据交换。

最后,值得注意的是,提供的状态转换图仅为基本示例,实际应用中可能需要考虑多个簇、片内终结电阻的选择、不同断电状态的进出等复杂情况,这些细节不在图示中详述,因此在设计FPGA接口时应参考相关规格文档和时序图表,以确保内存操作的正确性和稳定性。

105 浏览量

148 浏览量

115 浏览量

2019-02-06 上传

338 浏览量

265 浏览量

2025-03-06 上传

2025-03-06 上传

2025-03-06 上传

极光123

- 粉丝: 3

最新资源

- 计算机组成原理期末试题及答案(2011参考)

- 均值漂移算法深入解析及实践应用

- 掌握npm与yarn在React和pg库中的使用

- C++开发学生信息管理系统实现多功能查询

- 深入解析SIMATIC NET OPC服务器与PLC的S7连接技术

- 离心式水泵原理与Matlab仿真教程

- 实现JS星级评论打分与滑动提示效果

- VB.NET图书馆管理系统源码及程序发布

- C#实现程序A监控与自动启动机制

- 构建简易Android拨号功能的应用开发教程

- HTML技术在在线杂志中的应用

- 网页开发中的实用树形菜单插件应用

- 高压水清洗技术在储罐维修中的关键应用

- 流量计校正方法及操作指南

- WinCE系统下SD卡磁盘性能测试工具及代码解析

- ASP.NET学生管理系统的源码与数据库教程