FPGA设计:乒乓操作、串并转换与流水线技术

需积分: 9 77 浏览量

更新于2024-08-05

收藏 285KB PDF 举报

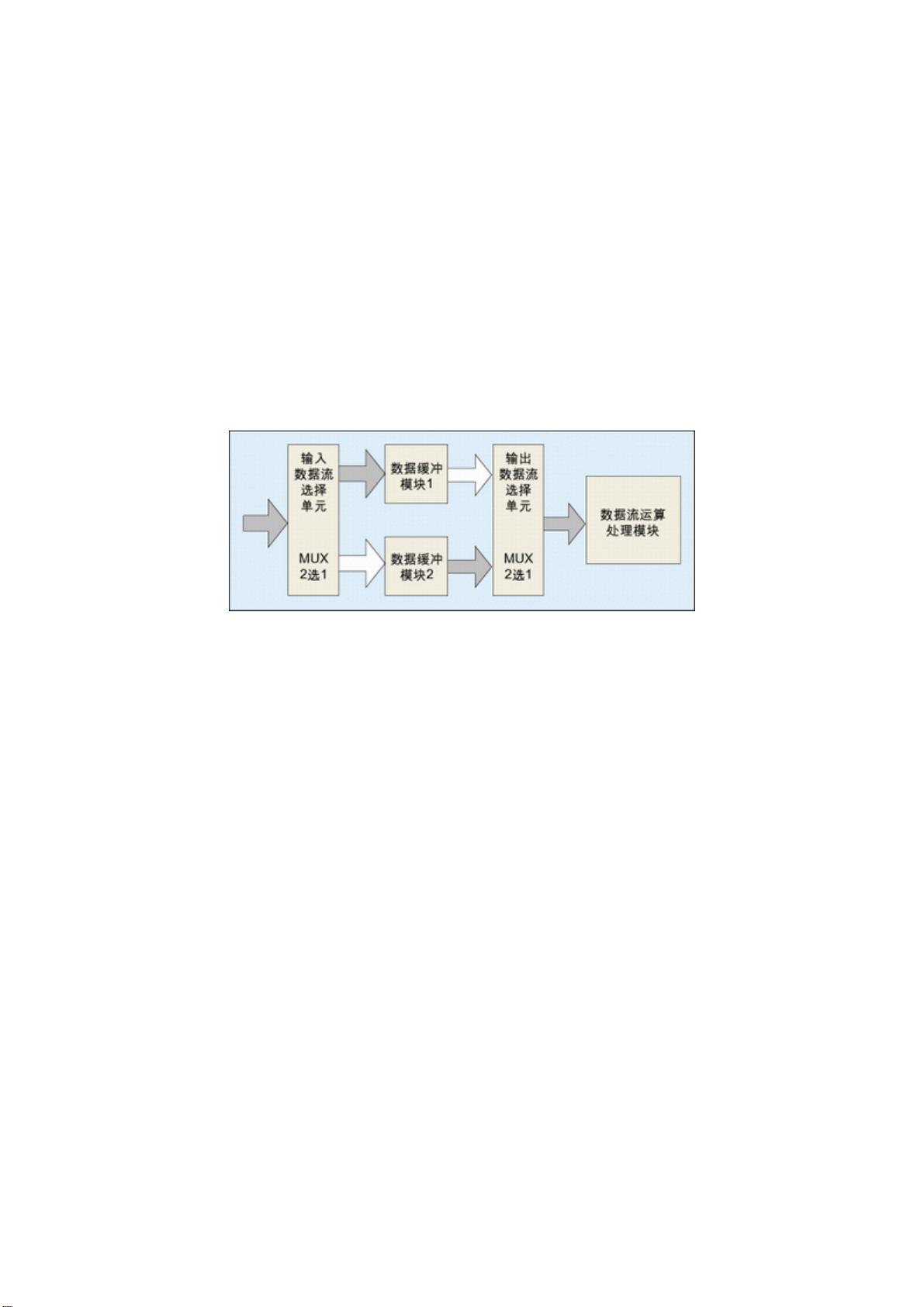

乒乓操作的实现通常依赖于FPGA内部的存储资源,如双口RAM或FIFO,它们能够在同一时钟周期内读写不同的数据,从而实现在处理过程中数据的无缝切换。这种技术在处理高吞吐量数据流时尤其有用,能够有效地提高系统性能。

串并转换(Serial-to-Parallel Conversion)

串行数据到并行数据的转换是FPGA设计中的常见操作,特别是在高速接口和数据传输场景中。例如,在接收高速串行数据时,为了将数据并行化以提高处理速度,可以使用串并转换器(Deserializer)。它在时钟域之间提供数据同步,并将连续的串行数据流转换为并行数据,通常在接收端进行。串并转换器通常包含移位寄存器和同步逻辑,确保数据在正确的时间被采样和处理。

流水线操作(Pipeline Operation)

流水线技术是FPGA设计中的核心优化策略,它将复杂任务分解为多个独立的阶段,每个阶段在不同的时钟周期内完成,从而实现连续的数据处理。流水线通过重叠各个阶段的计算,提高了系统的吞吐率,降低了延迟。例如,在图像处理或数字信号处理应用中,数据可以从输入端口进入,经过一系列处理阶段,最后从输出端口离开,每个阶段都在不同的时钟周期内完成其任务,使得整个系统能够连续无阻塞地处理数据。

数据接口同步化

在多模块的FPGA设计中,数据接口的同步化至关重要,因为不同的模块可能工作在不同的时钟域,需要通过同步机制来确保数据的准确传递。常见的同步方法包括边沿检测、双口RAM以及握手协议。例如,使用边沿检测可以在一个时钟域的上升沿捕获数据,在另一个时钟域的上升沿发送,确保数据在正确的时钟边界传输。握手协议则允许发送方和接收方通过信号进行通信,确认数据已经被正确接收,避免数据丢失或错误。

FPGA设计中,理解并灵活运用这些思想和技术,能够显著提升设计效率和系统性能。设计者需要考虑的因素包括资源利用率、功耗、时序约束以及系统的实时性要求。在实际设计中,可能还需要结合其他高级技术,如硬件描述语言(HDL)的优化、时钟管理、时序分析等,以达到最佳设计效果。同时,随着FPGA技术的发展,新的设计方法和工具不断涌现,持续学习和实践是保持竞争力的关键。

2023-02-26 上传

2023-02-27 上传

2023-02-26 上传

2023-09-17 上传

2023-06-23 上传

2023-09-28 上传

2023-12-04 上传

2023-06-21 上传

2023-02-19 上传

yongliu83

- 粉丝: 0

- 资源: 5

最新资源

- Flex 3 Cookbook中文版

- uf2008_WhyUDesign.pdf

- Oracle9i Database Error Messages.pdf

- RS232 通讯原理.doc

- Ubuntu实用学习手册

- SQL 语法教程不错

- 8051串口通信源程序

- 风中叶 cvs教程(浪曦)

- struts,spring,hibernate面试题

- 如何实现动态窗口的创建

- Addison.Wesley.MySQL.4th.Edition.Sep.2008

- vigeneer的加解密以及破译的代码

- FreeMarker中文文档

- Java学生成绩管理系统源代码

- WCDMA核心网及其演进

- 电子现金、电子信用卡、电子支票、网上银行和第三方支付的区别