VHDL实现:加法器、多路选择器与七段数码管

"该资源是关于EDA基础实验的,涵盖了加法器、多路选择器以及七段数码管的VHDL实现。通过十六位加法器、四位二选一多路选择器和七段数码管译码器的编程和仿真结果来展示EDA技术在数字逻辑设计中的应用。"

在电子设计自动化(EDA)领域,本实验提供了三个基本的数字逻辑组件的VHDL实现,分别是十六位加法器、四位二选一多路选择器和七段数码管译码器。

1. **十六位加法器**:在VHDL中,加法器是通过定义实体(ENTITY)和结构体(ARCHITECTURE)来实现的。实体`adder`有两个输入端口`A`和`B`,它们都是16位的二进制向量,一个输出端口`SUM`也是16位。结构体`behav`中,`SUM <= A + B;`这行代码表示了加法器的基本运算,即输出等于输入A和B的和。通过仿真,可以验证其正确性,确保加法器能正确执行16位的二进制加法。

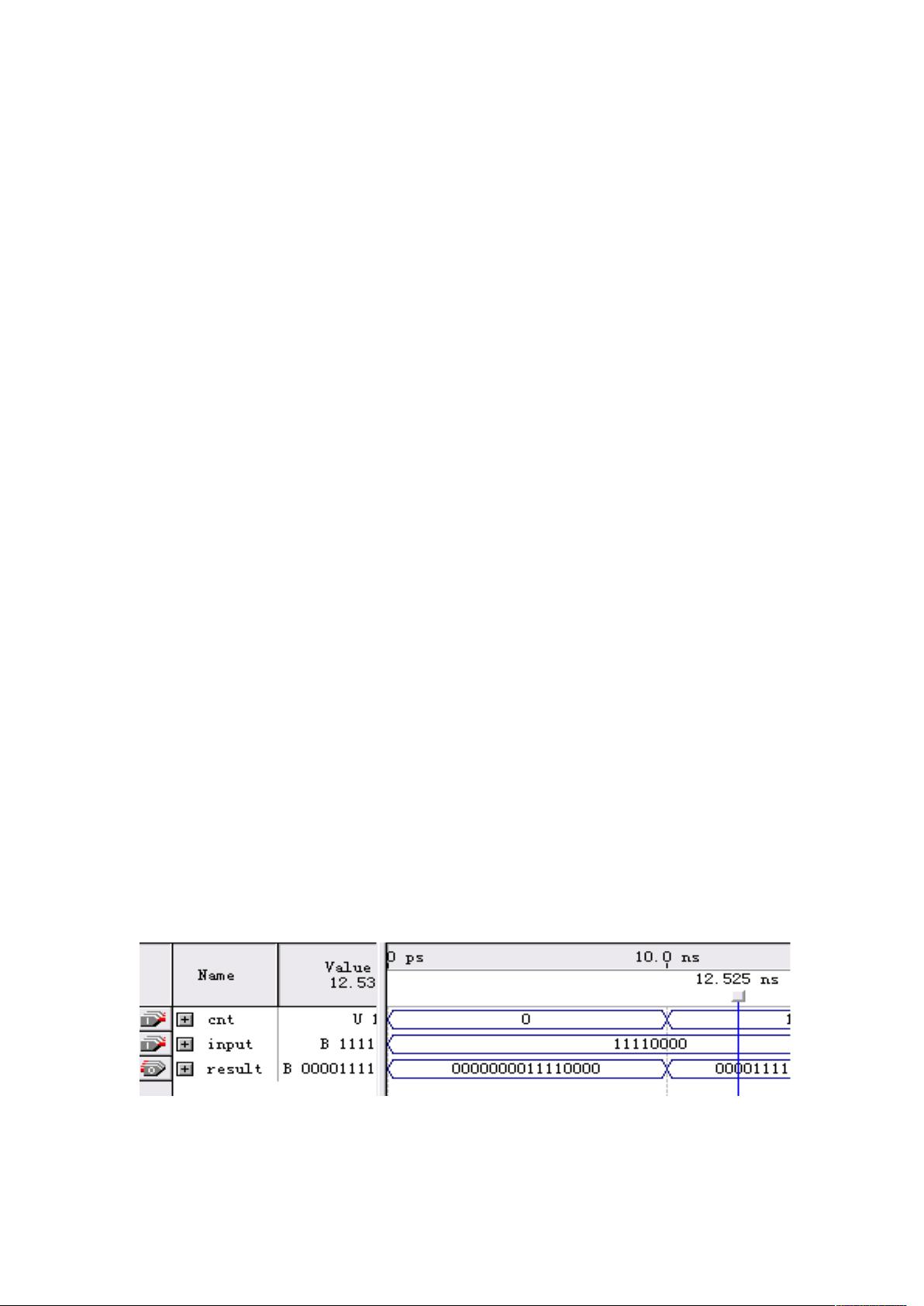

2. **四位二选一多路选择器**:多路选择器是一种能根据控制信号从多个输入中选择一个输出的设备。在这个例子中,`MUX4`是一个四位的二选一多路选择器,有四个数据输入端口`A`和`B`,一个选择输入`SEL`(整数范围0到1),和一个输出端口`Y`。当`SEL=0`时,输出`Y`取`A`的值,否则取`B`的值。通过进程(PROCESS)来实现条件判断,从而实现多路选择功能。

3. **七段数码管译码器**:七段数码管译码器是将二进制或BCD编码转换为七段显示的装置。实体`LED7`接收一个三位二进制输入`INPUT`,并有七个输出`A`到`G`对应七段数码管的七个部分。通过进程`PROCESS(INPUT)`和CASE语句,根据不同的输入值设置对应的七段显示。实验提供了从000到011的几种情况,以显示不同数字的七段码。

这些基础组件是数字系统设计的基础,通过VHDL语言进行描述,可以方便地在硬件描述语言环境中进行仿真和综合,最终实现到实际的FPGA或ASIC芯片上。这个实验对于理解和掌握EDA工具,以及数字逻辑设计原理具有重要的实践意义。

141 浏览量

1126 浏览量

353 浏览量

193 浏览量

2024-09-28 上传

2024-12-29 上传

184 浏览量

2025-03-12 上传

114 浏览量

wobushizhuliye

- 粉丝: 0

最新资源

- 立即体验无需安装的Virtual Drive Manager绿色软件

- SQLMemTable 3.05:无需BDE的快速内存数据库系统

- 精品Zencart模板下载集合,数十款精选设计

- 打造类似网易新闻的Android侧滑菜单功能

- Java源码实战:SipDemo数据插入技巧探究

- Source Insight代码美化新利器 - AStyle_3.1 for Windows

- 企业信息化风险管理:IT规划的必要性与实施策略

- DevOps CI/CD管道实现指南与工具集成

- Java实现高效学生管理系统开发指南

- 全新屏幕录像专家V2011版发布,注册教程一站式获取

- 使用WebBrowser组件在Android上打造简易浏览器教程

- Java POP3邮箱存储单元测试案例分析

- DB2认证考试必备:730、731、734完整资料包

- MATLAB实现Harris算法图像拼接教程

- 探索心理学中的关联方法与更正技术

- 09年文都考研数学全套资料:高数、线代与概率