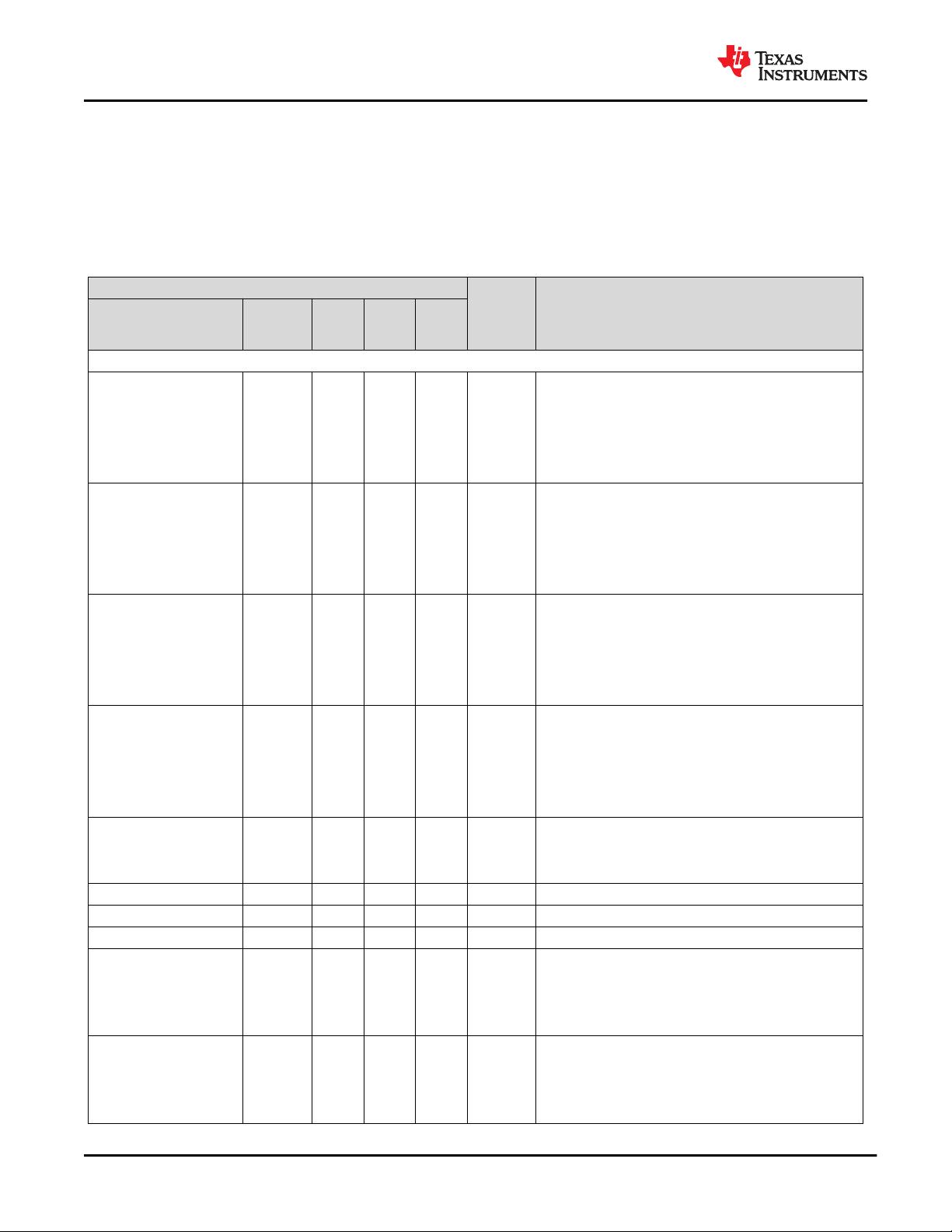

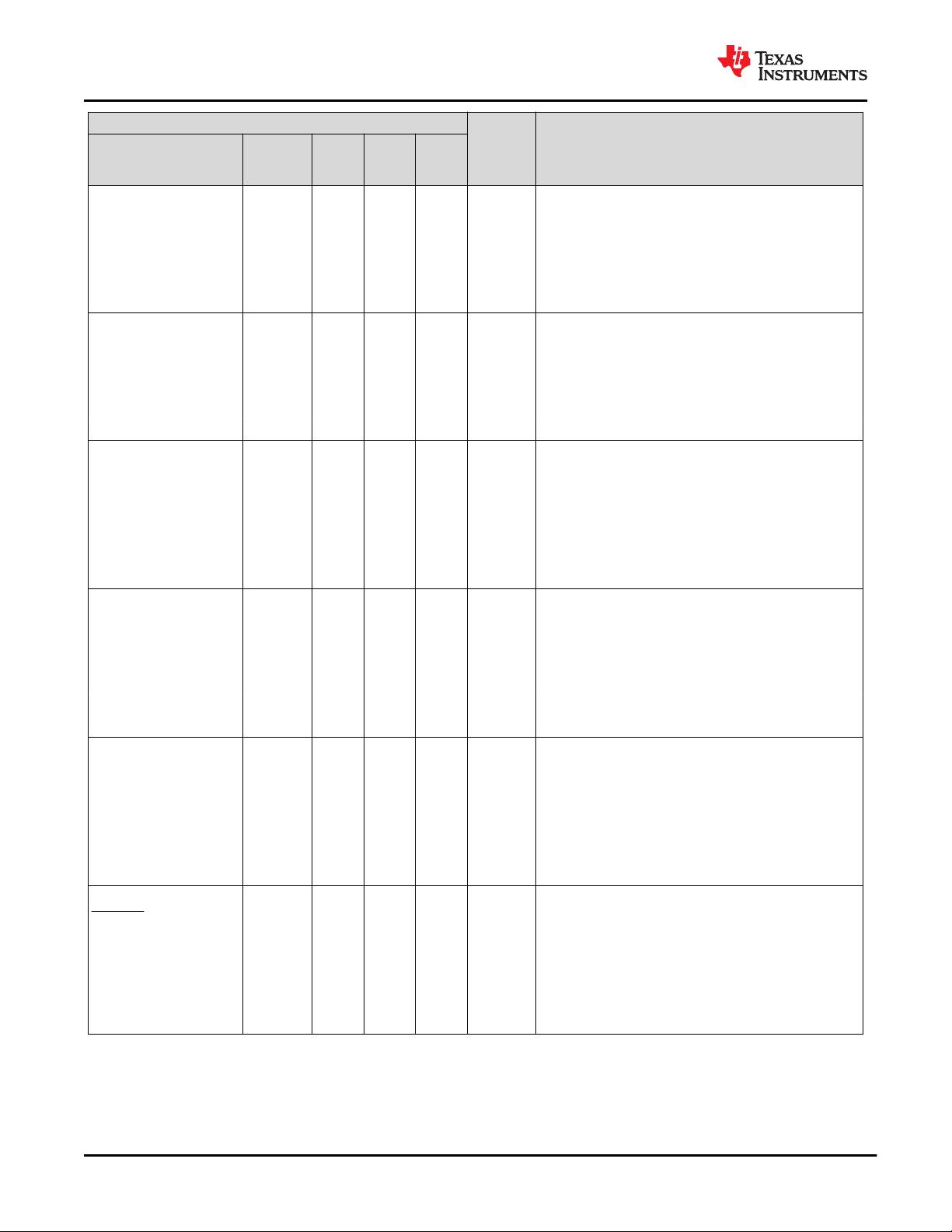

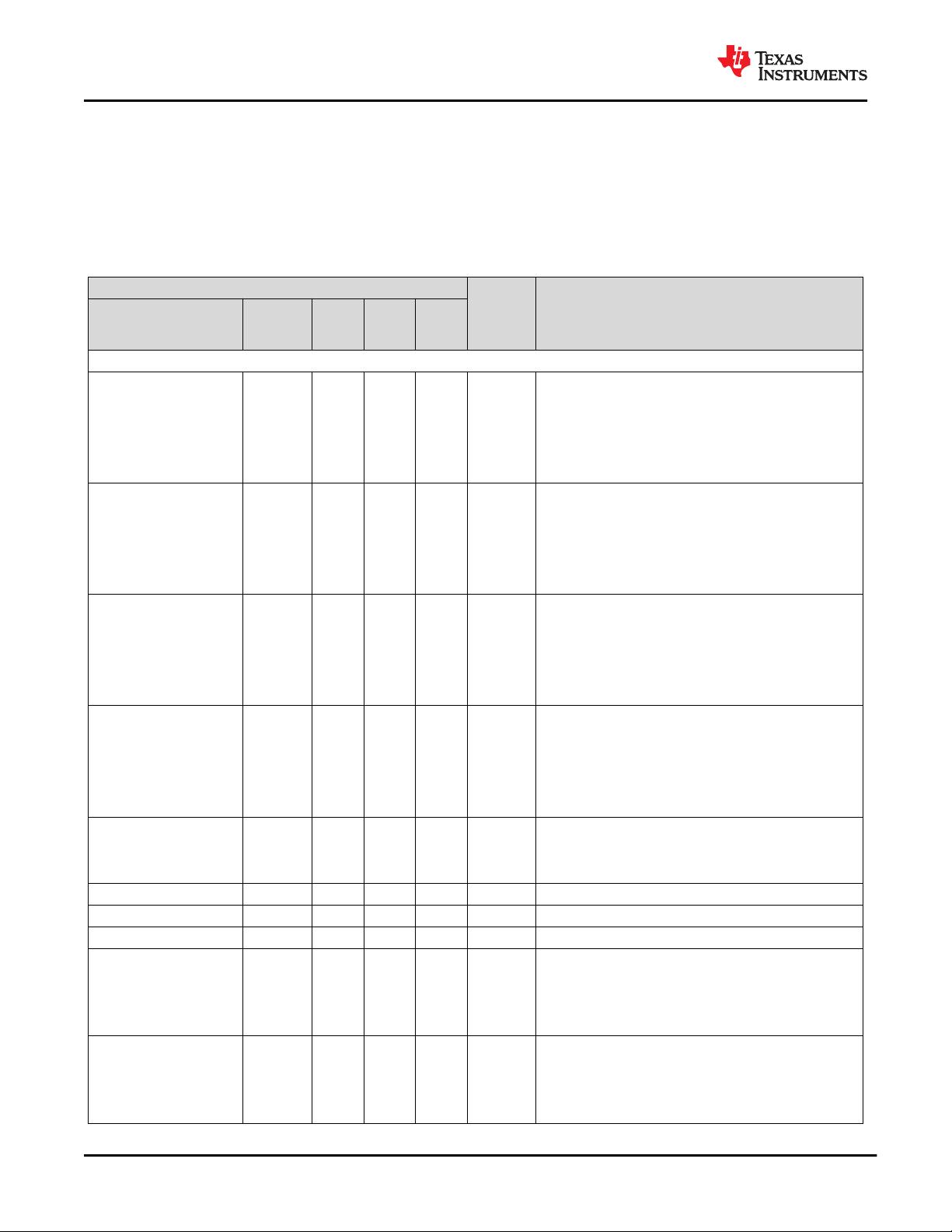

6.2 Signal Descriptions

Section 6.2.1 describes the signals. The GPIO function is the default at reset, unless otherwise mentioned. The

peripheral signals that are listed under them are alternate functions. Some peripheral functions may not be

available in all devices. See Table 5-1 for details. All GPIO pins are I/O/Z and have an internal pullup, which can

be selectively enabled or disabled on a per-pin basis. This feature only applies to the GPIO pins. The pullups are

not enabled at reset.

6.2.1 Signal Descriptions

TERMINAL

I/O/Z

(1)

DESCRIPTION

NAME

MUX

POSITION

ZWT

BALL

NO.

PTP

PIN

NO.

PZP

PIN

NO.

ADC, DAC, AND COMPARATOR SIGNALS

V

REFHIA

V1 37 19 I

ADC-A high reference. This voltage must be driven into

the pin from external circuitry. Place at least a 1-µF

capacitor on this pin for the 12-bit mode, or at least a 22-

µF capacitor for the 16-bit mode. This capacitor should be

placed as close to the device as possible between the

V

REFHIA

and V

REFLOA

pins.

NOTE: Do not load this pin externally.

V

REFHIB

W5 53 37 I

ADC-B high reference. This voltage must be driven into

the pin from external circuitry. Place at least a 1-µF

capacitor on this pin for the 12-bit mode, or at least a 22-

µF capacitor for the 16-bit mode. This capacitor should be

placed as close to the device as possible between the

V

REFHIB

and V

REFLOB

pins.

NOTE: Do not load this pin externally.

V

REFHIC

R1 35 – I

ADC-C high reference. This voltage must be driven into

the pin from external circuitry. Place at least a 1-µF

capacitor on this pin for the 12-bit mode, or at least a 22-

µF capacitor for the 16-bit mode. This capacitor should be

placed as close to the device as possible between the

V

REFHIC

and V

REFLOC

pins.

NOTE: Do not load this pin externally.

V

REFHID

V5 55 – I

ADC-D high reference. This voltage must be driven into

the pin from external circuitry. Place at least a 1-µF

capacitor on this pin for the 12-bit mode, or at least a 22-

µF capacitor for the 16-bit mode. This capacitor should be

placed as close to the device as possible between the

V

REFHID

and V

REFLOD

pins.

NOTE: Do not load this pin externally.

V

REFLOA

R2 33 17 I

ADC-A low reference.

On the PZP package, pin 17 is double-bonded to V

SSA

and V

REFLOA

. On the PZP package, pin 17 must be

connected to V

SSA

on the system board.

V

REFLOB

V6 50 34 I ADC-B low reference

V

REFLOC

P2 32 – I ADC-C low reference

V

REFLOD

W6 51 – I ADC-D low reference

ADCIN14

T4 44 26

I Input 14 to all ADCs. This pin can be used as a general-

purpose ADCIN pin or it can be used to calibrate all ADCs

together (either single-ended or differential) from an

external reference.

CMPIN4P I Comparator 4 positive input

ADCIN15

U4 45 27

I Input 15 to all ADCs. This pin can be used as a general-

purpose ADCIN pin or it can be used to calibrate all ADCs

together (either single-ended or differential) from an

external reference.

CMPIN4N I Comparator 4 negative input

TMS320F28379S, TMS320F28378S, TMS320F28377S, TMS320F28377S-Q1

TMS320F28376S, TMS320F28375S, TMS320F28375S-Q1, TMS320F28374S

SPRS881J – AUGUST 2014 – REVISED FEBRUARY 2021

www.ti.com

16 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TMS320F28379S TMS320F28378S TMS320F28377S TMS320F28377S-Q1

TMS320F28376S TMS320F28375S TMS320F28375S-Q1 TMS320F28374S