DSP考试重点:C5402内部结构与哈佛结构解析

需积分: 25 91 浏览量

更新于2024-10-28

5

收藏 152KB DOC 举报

"这份文档是针对DSP(数字信号处理)课程的一份期末考试题,涵盖了C5402 DSP芯片的相关知识,包括其内部总线结构、计算机体系结构的比较、流水线技术、存储空间的分配与访问控制信号,以及芯片的功能部件和中断系统等核心概念。"

1. **C5402的内部总线结构**:C5402 DSP拥有8组16位总线,包括1组程序总线PB,3组数据总线CB、DB、EB,以及4组地址总线PAB、CAB、DAB、EAB。CB和DB用于读取数据,EB用于写入数据。

2. **哈佛结构与冯·诺依曼结构的区别**:冯·诺依曼结构采用单存储空间,程序指令和数据共享存储,通过单一的地址和数据总线分时取指令和操作数。而哈佛结构则将程序存储器和数据存储器分开,有独立的程序总线和数据总线,允许同时访问。

3. **流水线技术**:流水线技术使得指令处理可以在多个阶段并行进行,如预取指、取指、译码、寻址、读数和执行,使得串行结构能实现并行效果,提高处理速度。

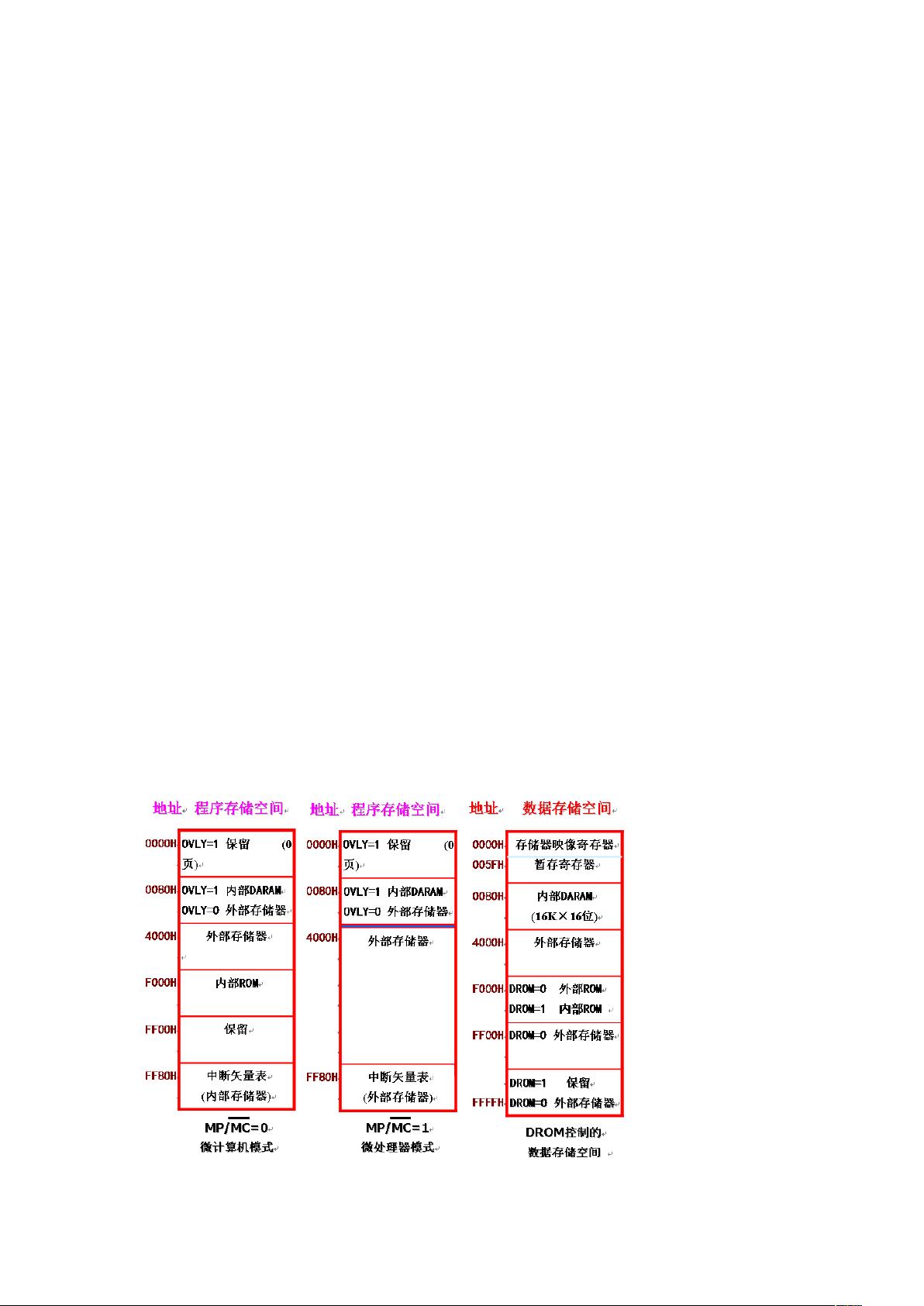

4. **C5402 DSP的存储空间**:C5402的程序空间、数据空间和I/O空间都为64K字。其分配由MP/MC和OVLY控制位决定,MP/MC决定微处理器工作模式,OVLY决定程序存储空间是否使用内部RAM。

5. **访问控制信号**:外部程序存储空间的访问由/PS、/MSTRB、R/W控制;外部数据存储空间由/DS、/MSTRB、R/W控制;外部I/O空间由/IOSTRB、/IS和R/W控制。

6. **C5402的功能部件**:包括通用I/O引脚、定时器、时钟发生器、主机接口HPI、串行通信接口、软件可编程等待状态发生器和可编程分区转换逻辑。

7. **流水线操作阶段**:C5402的流水线操作包括预取指、取指、译码、寻址、读数和执行,这些阶段可以并行工作,实现高效处理。

8. **硬件中断系统**:C5402支持可屏蔽中断和不可屏蔽中断,有13个可屏蔽中断,如外部中断/INT3~/INT0和串行口中断BRINT0、BXUNT0等。

这份资料详尽地测试了学生对C5402 DSP芯片的理解,包括其架构、存储管理、并行处理能力以及中断系统等多个关键领域,旨在评估学生的理论知识和实际应用能力。

2021-09-30 上传

2021-09-25 上传

2021-09-26 上传

2024-07-23 上传

2021-09-27 上传

2021-10-06 上传

daben5217758521

- 粉丝: 0

最新资源

- Fedora 10中文安装配置全面指南:新手必备

- Spring2.5开发简明教程:中文版入门与实践

- Access基础教程:从入门到实践

- ActionScript 3实战宝典:解决Web开发疑难问题

- Modelsim 6.0入门教程:功能仿真与安装详解

- SQL Server编程基础:T-SQL详解与实践

- IP网络上传真实时传输:ITU-T T.38协议详解

- SAP标准对话框函数:操作确认与数据输入指南

- 大学计算机C语言精选复习题集

- SunOne 7.0 WebServer管理员指南:安装与双认证详解

- ADS中文教程:ARM开发环境与调试详解

- GCC编译器参数详细解析

- LoadRunner负载测试工具详解与实战指南

- IIS与Access数据库实现简易留言本教程

- 电子技术基础课程设计详解:系统设计与单元电路构建

- FPGA智能太阳追踪系统设计提升发电效率