计数器与寄存器:数字系统设计中的关键时序逻辑器件

需积分: 9 86 浏览量

更新于2024-08-02

收藏 2.78MB PDF 举报

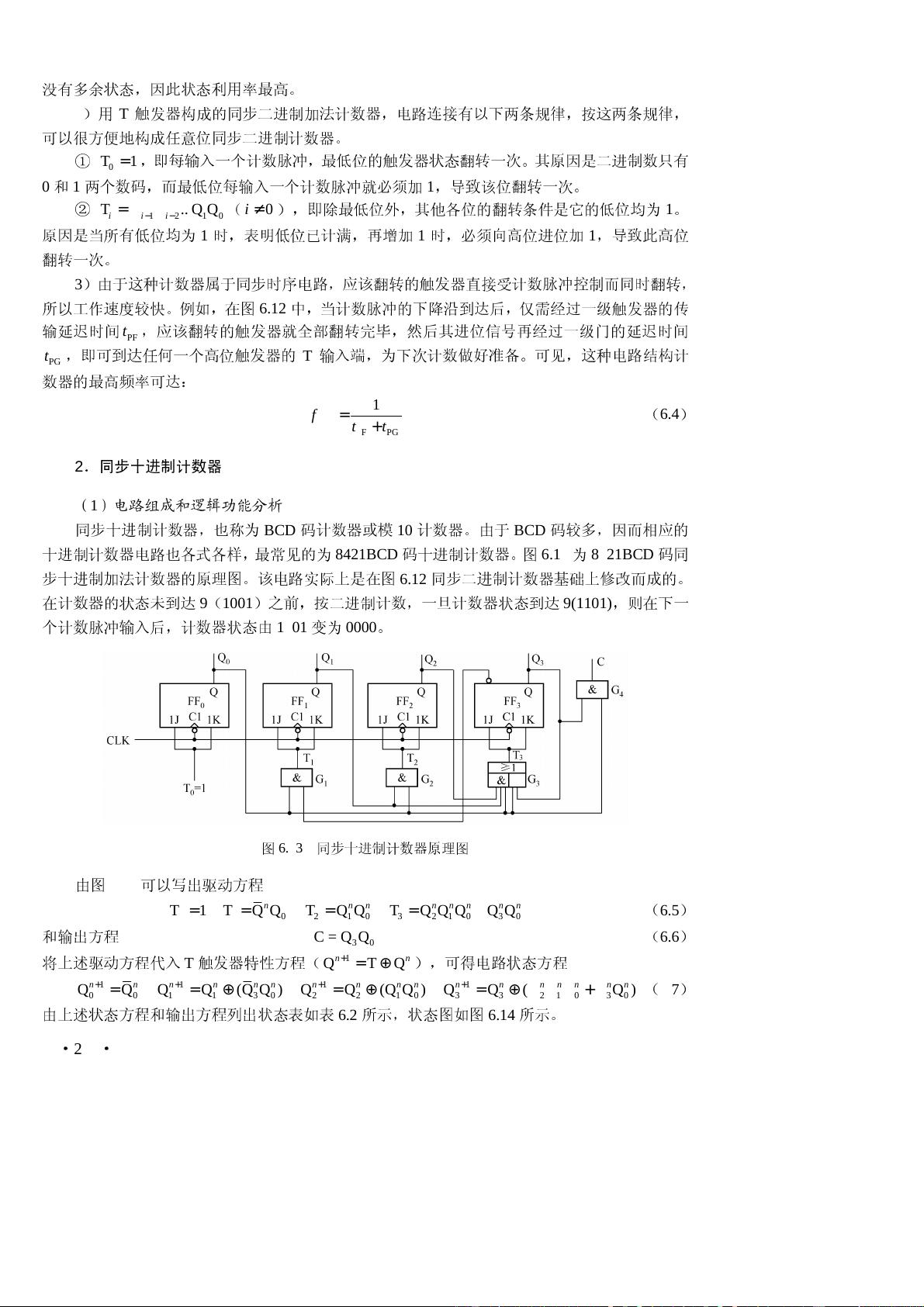

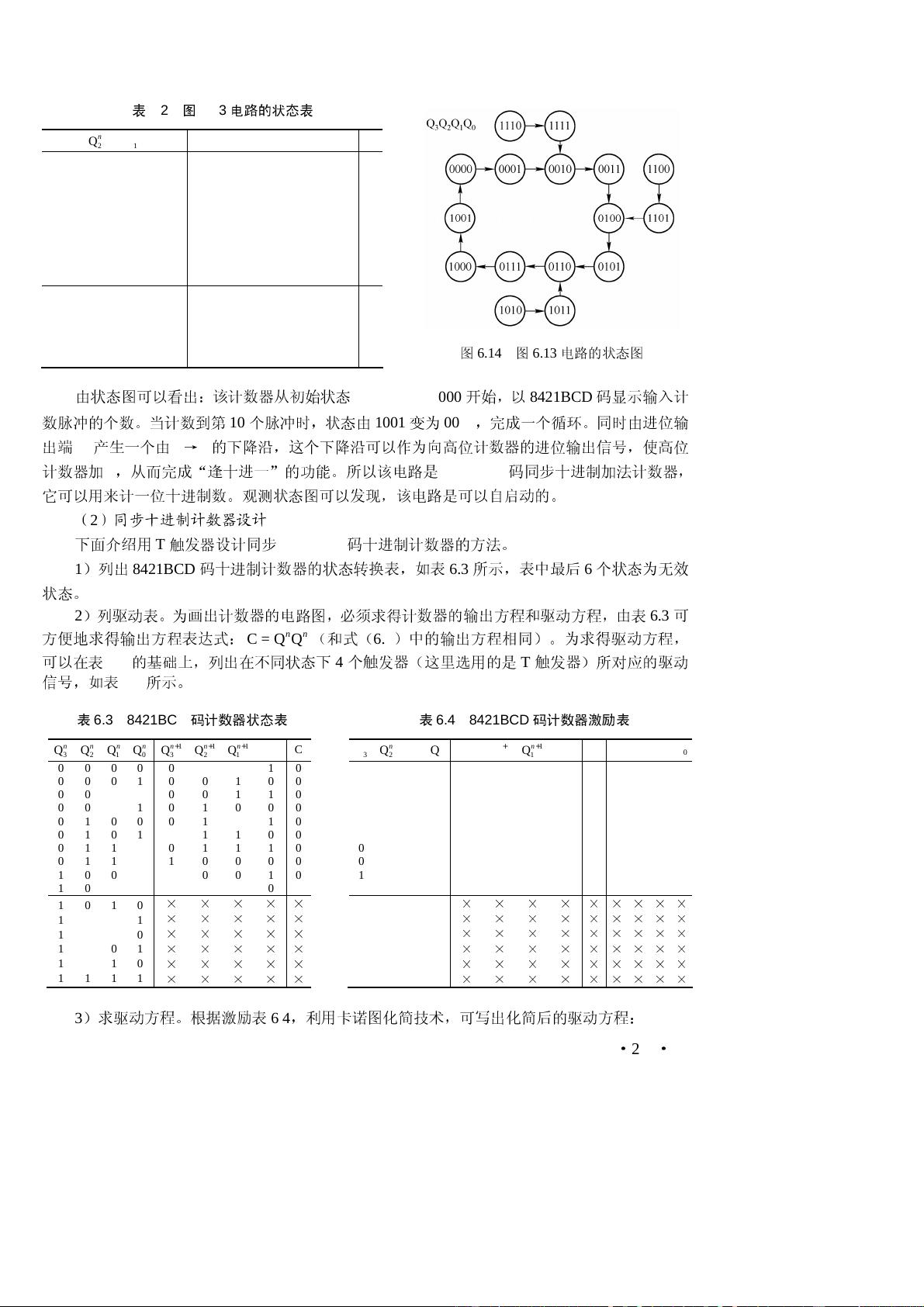

"常用时序逻辑功能器件,包括计数器和寄存器,是数字系统设计中的核心组件。计数器能统计输入脉冲数量,应用于计数、定时、分频、控制等多个领域。计数器按照计数脉冲的作用方式分为同步和异步,按进位基数分为二进制和非二进制。异步计数器中,触发器状态改变无全局同步,例如异步二进制计数器,通过负跳变触发状态转换,形成波浪式计数。"

在数字电子技术中,时序逻辑器件扮演着至关重要的角色,它们能够根据时钟信号和当前状态存储并处理信息。计数器是时序逻辑电路的一种,主要功能是统计输入脉冲的数量,这些脉冲可以是有序或无序的。计数器广泛应用于各种数字系统,如定时器、分频器、控制器和信号发生器,其灵活性使其成为设计中的通用部件。

计数器的分类主要基于两个标准:一是计数脉冲的作用方式,即同步和异步。同步计数器的所有触发器共享同一时钟信号,状态改变同步进行;而异步计数器的触发器状态改变可能是异步的,由输入脉冲直接控制或由其他触发器的输出触发。异步计数器的一个例子是行波计数器,其状态变化自低位向高位逐级推进。

另一种分类方式是基于进位基数,也就是模,分为二进制计数器和非二进制计数器。二进制计数器是最常见的,它们按照二进制数的规则增加或减少计数值。例如,4位异步二进制加法计数器,由4个JK触发器构成,低电平触发,触发器之间的状态转换由输入脉冲驱动,且无全局时钟同步,形成逐级推进的计数模式。

对于异步二进制计数器的分析,可以通过直观的方法进行。在开始计数前,先用负脉冲清零所有触发器,随后输入待计数的脉冲,每次脉冲都会引起最左侧触发器状态翻转,依次影响到更高位的触发器,这样就可以绘制出各触发器输出相对于时钟脉冲的波形图,展示出计数过程。

寄存器是另一类重要的时序逻辑器件,它能够存储数据并在时钟信号的控制下保持或传递数据。寄存器分为多种类型,如移位寄存器、存储寄存器等,它们在数据处理、缓冲和传输中起到关键作用。

VHDL是一种硬件描述语言,常用于描述和实现计数器和寄存器等数字逻辑系统。通过VHDL,设计师可以精确地定义计数器和寄存器的行为,便于在FPGA或ASIC等可编程逻辑器件上实现。

时序逻辑器件如计数器和寄存器是构建复杂数字系统的基础,它们的正确理解和应用对于电子工程师至关重要,无论是设计微处理器、嵌入式系统还是数字信号处理系统,都需要依赖这些基本的时序逻辑元件。

2010-06-18 上传

2021-09-21 上传

2021-09-20 上传

2023-02-05 上传

2024-09-10 上传

2024-11-24 上传

2023-05-15 上传

2022-01-26 上传

2024-04-15 上传

woshihwt

- 粉丝: 3

- 资源: 20

最新资源

- Software-company-ms1

- 简洁网站底部内容响应式网页模板

- 实现ROI选取、选框放缩移动、背景图像移动放缩

- matlab 对一个文件夹里的所有图像进行批量旋转90度并保存.rar

- 我的个人博客Sass-个人简介

- 多种扁平UIKIT组件响应式网页模板

- java源码查看工具-android_layout_xml_view_finder:使用该工具,您可以轻松地从给定的AndroidLayout

- jdk-8u151-windows-x64.zip

- Proyecto-1-Operativos-Brito-Ferreira:Proyecto 1 de la materia Sistemas Operativos。 整合对象:Brito,Nicole y Ferreira,Giselle

- STM32cubemx STM32F1系列 IIC双机通讯 主机程序

- libEasyPlayer测试项目及工具.rar.rar

- nextjs-blog:Next.js +内容丰富的博客应用程序

- OpenCV官网下载缺失文件

- AutomationSelenium:使用Selenium工具自动进行

- stylegan2-distillation

- ze