高速PCB设计:超越等长误区,重视时序与交互影响

需积分: 10 15 浏览量

更新于2024-07-14

收藏 2.49MB DOCX 举报

高速PCB设计是一个复杂而精细的过程,特别是在处理高速信号传输时。标题“高速PCB设计绕等长一定要绕个山路十八弯太算吊”实际上探讨了在现代高速PCB设计中,一味追求线长等长策略是否最优的问题。传统上,等长布局(length-matching routing)被作为降低串扰和保持信号完整性的基本方法,尤其是在早期DDR标准中占据重要地位。然而,随着技术的发展,如DDR II及更高速度等级的规范,设计规则发生了变化。

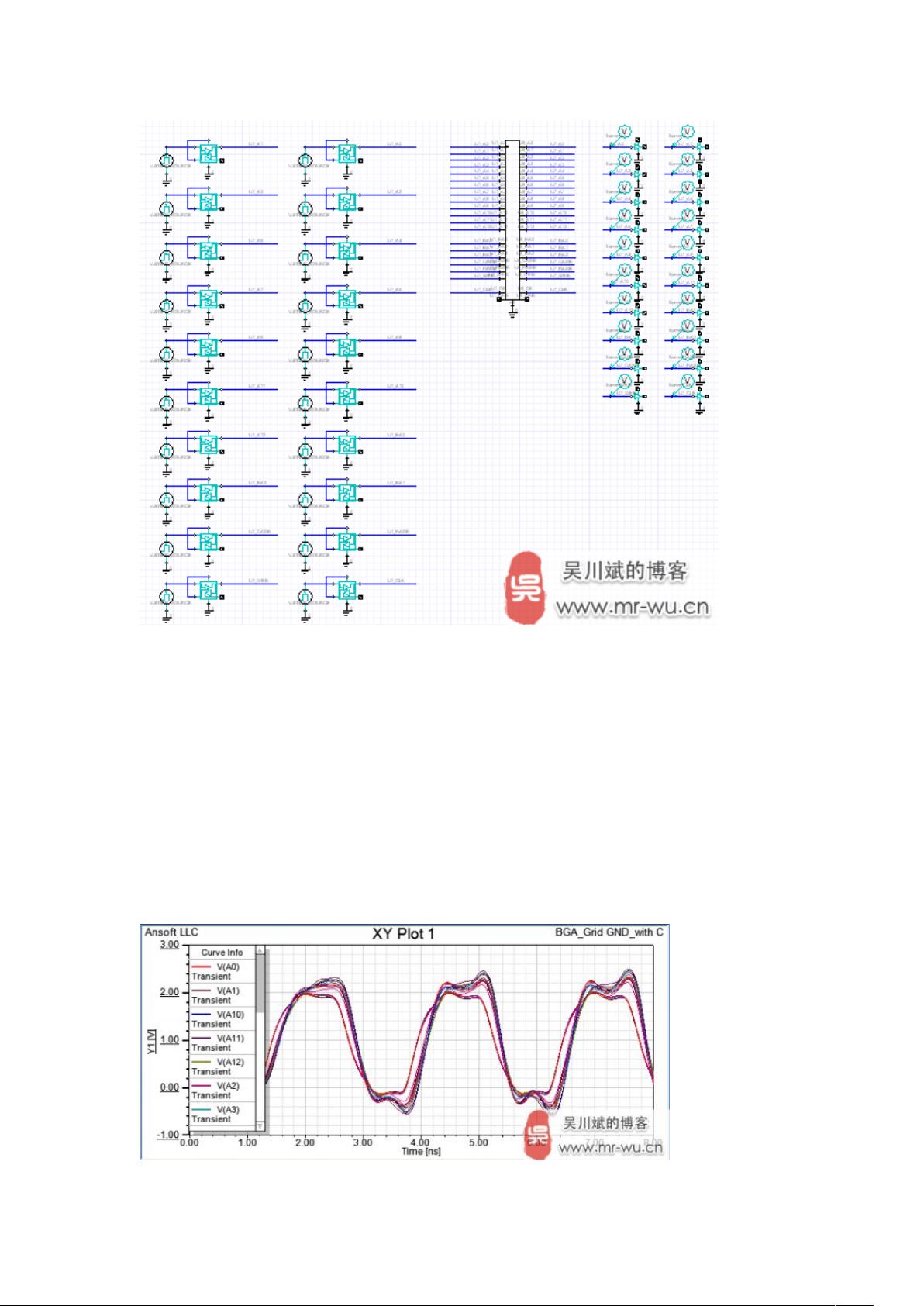

现在的焦点不再是单一的线长匹配,而是转向了建立有效的信号时序预算(setup time, hold time budget with jitter),这意味着设计师需要理解并应用时序图以及模拟技术来确保信号的性能。时序参数的满足比线长一致性更为关键,即使线长差异在一定程度上(如500mils)对信号完整性的影响较小,但整体线路的总长度增加,特别是通过多层板时,会显著增加信号延迟。

在高速PCB设计中,还有其他因素需要考虑,如stack-up(多层堆叠)、via(通孔)、stub(短线)、coplane(平面布线)和slot(槽孔)等,这些都会相互作用并对信号性能产生影响。例如,贯孔换层(thru-hole vias)和相邻孔的clearance hole(隔离垫)可能会破坏信号路径的连续性,从而影响信号质量。此外,蛇线(zigzag routing)虽然可以减少等长问题,但如果过度使用或导致总线长度过大,反而可能增加阻抗不连续性和邻线电容耦合效应,对信号稳定性产生负面影响。

因此,设计者应该寻求在满足设计规范的前提下,找到一个平衡点,比如使用最短的蛇线以保持合理的信号完整性,同时保持至少2W规则(对于DDR II,如果启用ODT,可能降低至1W)。地回路的连续性也是不可忽视的,因为它对电磁兼容性(EMI)有直接影响。

总结来说,现代高速PCB设计不再仅仅局限于简单的线长等长,而是需要综合考虑多种因素,包括时序、信号完整性、EMI和物理实现,以达到最佳性能。设计师需要灵活运用各种设计策略和技术,而不是拘泥于传统的规则,以适应不断发展的技术需求。

1194 浏览量

110 浏览量

lx5213

- 粉丝: 4

最新资源

- 实现键盘鼠标消息的记录与回放功能

- C# VS2010串口调试新手学习实例源码

- 3D MAX场景管理新助手:场景助手4.1.1发布

- 新手友好的Android任务管理器功能详解

- Python自动化脚本:拆分视频与焦距估算工具

- 2018年今日头条技术面试题分享

- 企业级网站ASP源码及管理员密码加密解密技术

- C++实现狼羊过河问题与动态解决方案

- 优化CSS属性与浏览器兼容性实现高效网页布局

- Session购物车项目实现:记录商品浏览与数据库交互

- 使用Perl5实现剪贴板内容处理的简易教程

- RMAN异机恢复方法与实践详析

- ReFX Nexus 2中文手册:全面使用教程指南

- DV-HOP算法在无线传感器网络定位中的MATLAB仿真

- 探索XPCOM在跨平台程序开发中的应用

- Office2007文件轻松转换为PDF格式教程