Cypress CY7C144E:8K×8双端口静态RAM,带仲裁和信号功能

需积分: 9 180 浏览量

更新于2024-07-10

收藏 552KB PDF 举报

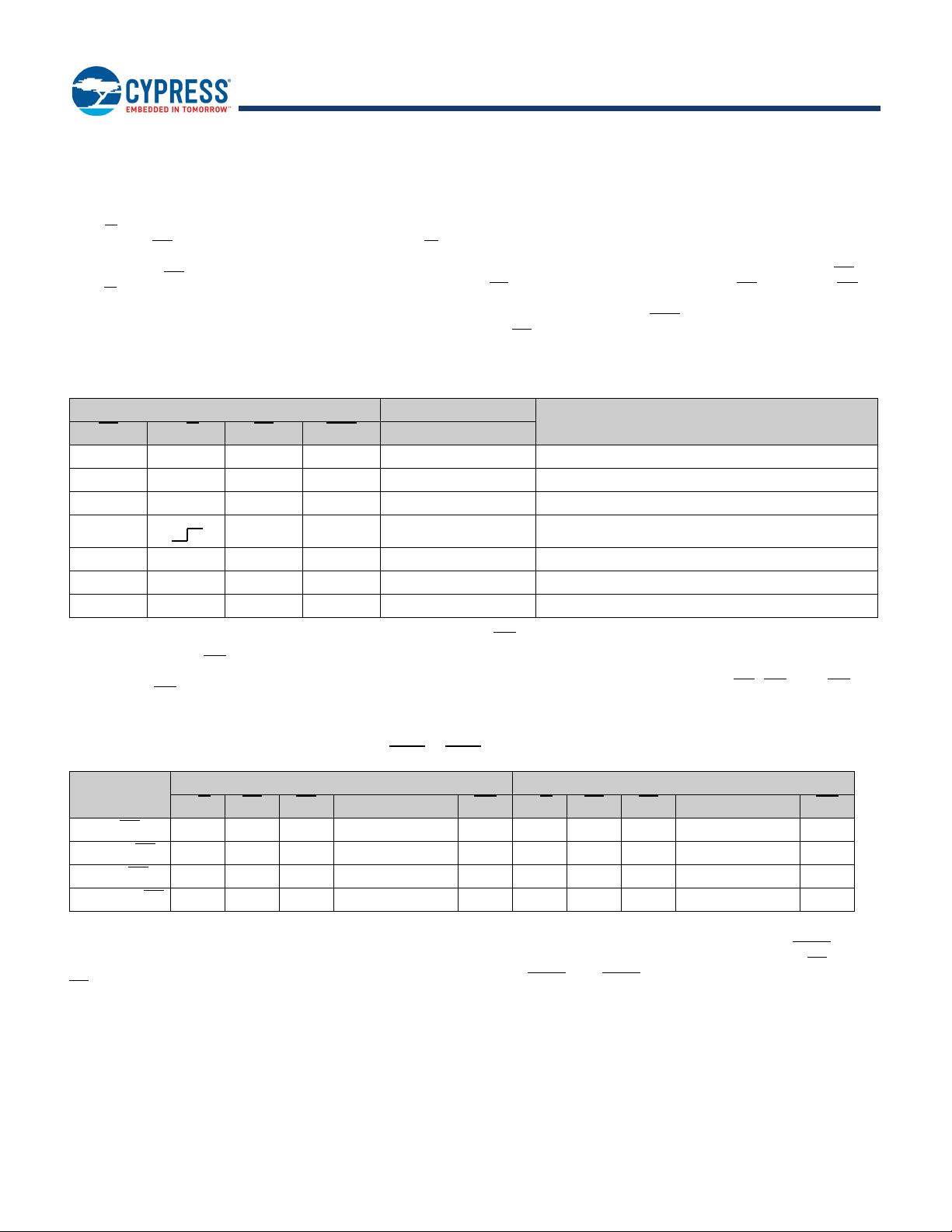

"CYPRESS-CY7C144E-55JXC.pdf 是 Cypress Semiconductor Corporation 生产的一款8K×8双口静态RAM,具备同时读取相同内存位置的真正双端口存储单元、0.35微米CMOS工艺、15ns高速访问、低功耗操作以及多种功能特性,适用于需要高效能和高并发数据处理的应用场景。"

该器件的主要特点包括:

1. **真正双端口内存单元**:CY7C144E具有真正的双端口内存设计,允许两个独立的读写端口在同一时刻对同一内存位置进行读取或写入操作,提高了数据访问效率。

2. **8K×8组织结构**:该芯片的存储容量为8K字节(即64K位),每字节包含8位,提供充足的存储空间。

3. **0.35微米CMOS工艺**:采用先进的0.35微米CMOS工艺,确保了高速度和低功耗的性能。

4. **高速访问**:数据访问速度达到15ns,满足高速数据处理的需求。

5. **低功耗**:正常工作时的电流消耗为180mA(典型值),待机状态下电流消耗仅为0.05mA(典型值)。

6. **完全异步操作**:所有操作与系统时钟无关,提高系统的灵活性。

7. **自动电源关闭**:在无活动时,器件能够自动进入低功耗模式,节省能源。

8. **TTL兼容**:与TTL逻辑电平兼容,方便与其他TTL电路集成。

9. **主/从选择引脚**:支持主/从模式,可扩展总线宽度至16位或更大,便于构建更宽的数据通道。

10. **仲裁机制**:内置仲裁策略,处理多个处理器同时访问相同数据的情况,避免冲突。

11. **信号量(Semaphore)**:通过信号量实现端口间的软件握手,确保数据访问的有序性。

12. **INT标志**:提供了端口间通信的中断标志,用于通知端口状态变化。

13. **封装选项**:提供68引脚PLCC和64引脚TQFP两种封装形式,适应不同设计需求。

14. **无铅封装**:也有无铅封装版本,符合环保要求。

CY7C144E是一款高性能、低功耗的8K×8双端口静态RAM,适用于需要高速、并发数据处理的嵌入式系统,如多处理器系统、通信设备和实时控制系统等。其丰富的功能和灵活的设计使其成为解决复杂数据同步和共享问题的理想选择。

2021-04-28 上传

2009-07-08 上传

2021-04-28 上传

2021-04-28 上传

2021-04-28 上传

2008-05-13 上传

2021-04-28 上传

2021-04-28 上传

2011-10-11 上传

LC灵灵

- 粉丝: 1

- 资源: 261

最新资源

- 开源通讯录备份系统项目,易于复刻与扩展

- 探索NX二次开发:UF_DRF_ask_id_symbol_geometry函数详解

- Vuex使用教程:详细资料包解析与实践

- 汉印A300蓝牙打印机安卓App开发教程与资源

- kkFileView 4.4.0-beta版:Windows下的解压缩文件预览器

- ChatGPT对战Bard:一场AI的深度测评与比较

- 稳定版MySQL连接Java的驱动包MySQL Connector/J 5.1.38发布

- Zabbix监控系统离线安装包下载指南

- JavaScript Promise代码解析与应用

- 基于JAVA和SQL的离散数学题库管理系统开发与应用

- 竞赛项目申报系统:SpringBoot与Vue.js结合毕业设计

- JAVA+SQL打造离散数学题库管理系统:源代码与文档全览

- C#代码实现装箱与转换的详细解析

- 利用ChatGPT深入了解行业的快速方法论

- C语言链表操作实战解析与代码示例

- 大学生选修选课系统设计与实现:源码及数据库架构