"TI-PCA9515A.pdf: I2C缓冲器,支持不同封装类型"

需积分: 0 61 浏览量

更新于2024-01-05

5

收藏 1.51MB PDF 举报

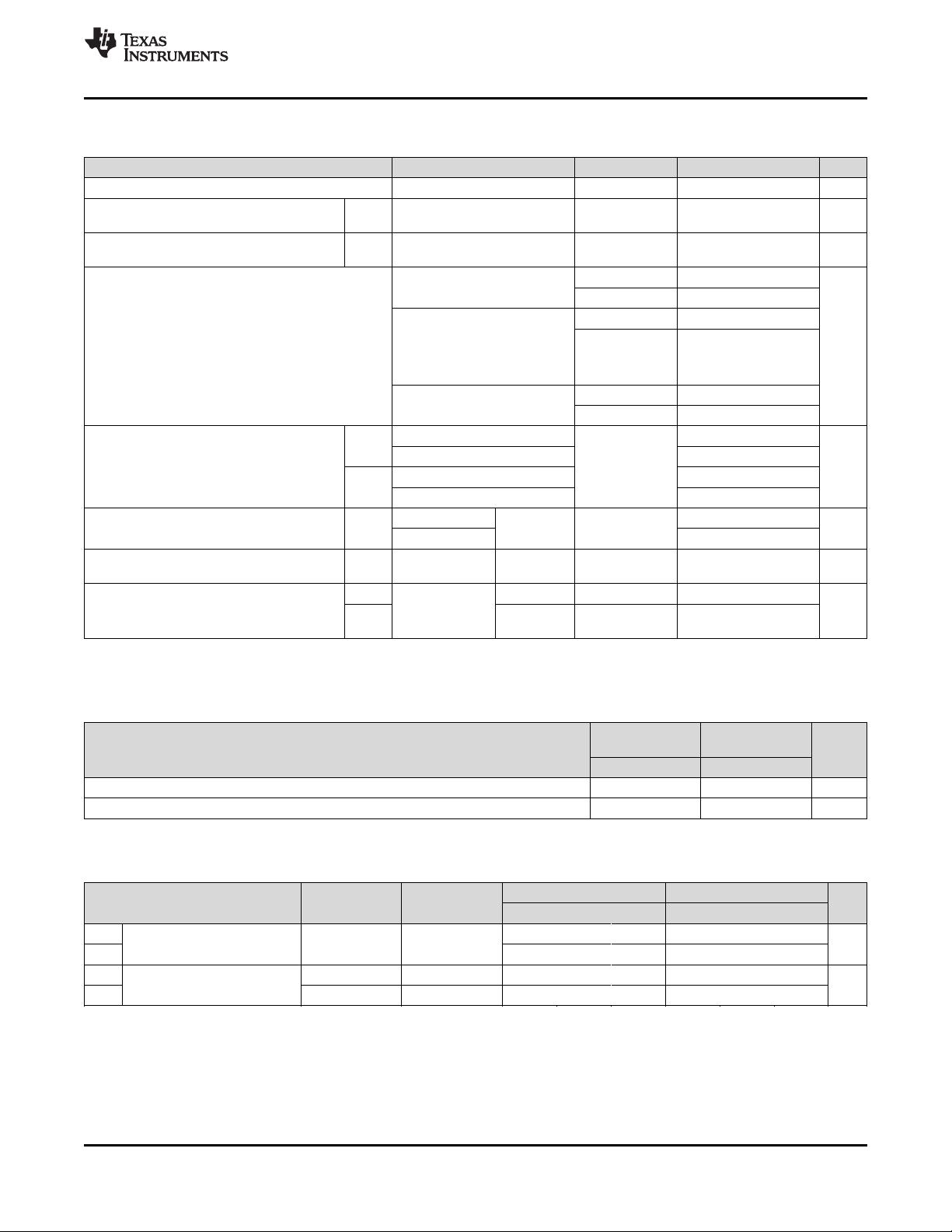

The TI-PCA9515A.pdf is a document that provides information on the I2C buffer, which is a useful device for buffering the I2C bus signals. The document specifies the pin configuration of the device in various package options, such as D, DCT, DGK, OR PW package, and DRG package.

In the D, DCT, DGK, OR PW package, the pin configuration is as follows when viewed from the top:

1. VCC: This pin is used to supply power to the device.

2. SCL1: This pin is connected to the I2C clock line from the master device.

3. SDA1: This pin is connected to the I2C data line from the master device.

4. EN: This pin is used to enable the buffer. When enabled, it allows the I2C signals to pass through.

5. N.C.: This pin stands for "No connection" and is not internally connected.

6. SCL0: This pin is connected to the I2C clock line from the slave devices.

7. SDA0: This pin is connected to the I2C data line from the slave devices.

8. GND: This pin is used as the ground reference for the device.

In the DRG package, the pin configuration is similar to the previous package, except for the absence of the N.C. pin.

The document also provides a product folder and a sample to allow users to further explore the features and functionality of the TI-PCA9515A I2C buffer.

Overall, the TI-PCA9515A.pdf is a comprehensive guide that provides essential information on the I2C buffer. It includes details on the pin configuration in different package options, allowing users to select the appropriate package for their application. The document serves as a valuable resource for understanding and utilizing the TI-PCA9515A I2C buffer effectively.

2023-02-07 上传

2023-02-01 上传

117 浏览量

2023-02-08 上传

175 浏览量

2023-02-08 上传

2023-02-08 上传

2023-02-07 上传

2023-02-07 上传

不觉明了

- 粉丝: 7733

- 资源: 5764