中兴GTP基础功能配置教程:时钟与接口详解

需积分: 32 192 浏览量

更新于2024-09-09

收藏 1.32MB DOC 举报

GTP(Generic Tile Processor)是一种高度可配置的硬件加速引擎,广泛应用于中兴的FPGA设计中。其基本功能的使用方法主要涉及以下几个方面:

1. **模块实例化**:

在设计中集成GTP,首先需要将CoreGenerator生成的src目录下的XXXtile.v模块作为自定义硬件单元实例化到你的FPGA设计的顶层代码中。这样,你的系统就可以利用GTP提供的计算能力。

2. **组成部分与设置**:

GTP由多个可选和必选功能模块构成,如时钟管理、TXinterface和RXinterface等。每个模块的设置包括:

- **时钟设置**:GTP工作在tile级别,每个tile有两个GTP单元,每个包含一个接收器和发送器。时钟源有三种:专用引脚、与其他tile共享(避免时钟域重叠)以及片内逻辑产生的时钟(不推荐,可能导致抖动和偏移)。在CoreGenerator中,仅需设定线速率和内部数据宽度,软件会自动计算合适的时钟频率,如选择122.88MHz作为2.4576Gbps TDM模块的CLKIN。

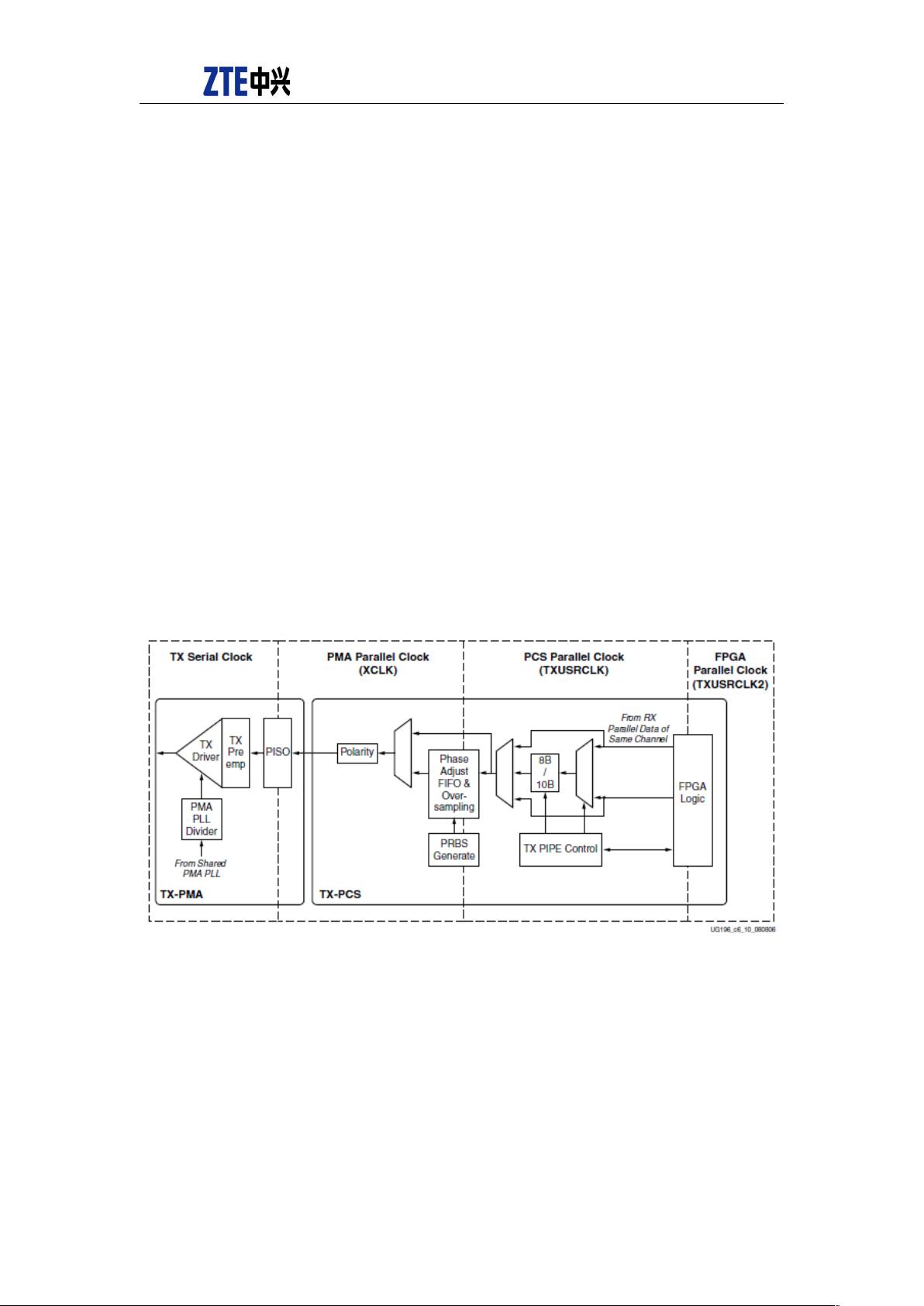

3. **TXinterface**:

TXinterface是GTP与用户自定义逻辑的接口,支持8、16、10、20位数据传输。数据在TXUSRCLK2上升沿写入,期间涉及两个时钟域:TXUSRCLK(与TXUSRCLK2关系取决于数据位宽,如果是8或10位则相同,16或20位则频率翻倍)。TXUSRCLK2与TXUSRCLK需要同步,且两者都应由同一个时钟源驱动,可以通过REFCLKOUT分频或者使用TXOUTCLK来实现。

4. **参数设置**:

参数设置包括GTP的端口配置,这些配置可能涉及到数据宽度、时钟配置、编码方式等。CoreGenerator工具提供了一种便捷的方式来完成这些设置,使得用户可以根据具体应用需求灵活调整。

5. **注意事项**:

- 时钟共享需谨慎,确保时钟域的独立性和正确性。

- 选择合适的时钟频率对于性能和稳定性至关重要。

- 接口设计时要考虑到数据位宽和时钟同步问题。

使用GTP的基本功能时,关键在于理解并正确配置其模块和接口,以适应特定的应用场景。通过熟悉其模块构成、时钟管理以及接口设置,开发者可以高效地集成GTP到FPGA设计中,从而提升系统的性能和效率。

298 浏览量

216 浏览量

2021-03-27 上传

2016-05-10 上传

220 浏览量

2021-10-06 上传

126 浏览量

126 浏览量

1613 浏览量

方槍槍

- 粉丝: 2

- 资源: 19