CMOS数字集成电路:时序分析与钟频不稳定性

需积分: 9 137 浏览量

更新于2024-07-19

收藏 1.32MB PDF 举报

"CMOS数字集成电路的第七章课件,主要讲解了时序相关的概念,由成均馆大学的Yoonmyung Lee教授提供。内容涵盖了同步时序、时钟不确定性、时钟非理想性(如时钟偏斜和抖动)以及与之相关的挑战。"

在数字集成电路设计中,时序分析是至关重要的,因为这直接影响到电路的性能和可靠性。本课件主要探讨了以下几个关键知识点:

1. **同步时序**:在数字系统中,大多数时序电路是同步工作的,这意味着它们的操作基于一个共同的时钟信号。这个时钟信号控制着数据的采样和传输,确保逻辑门和寄存器在同一时间点进行操作,从而保证数据的正确流动。

2. **时钟不确定性**:时钟信号的不确定性是数字系统设计中的一个主要考虑因素,它包括电源波动、互连延迟、温度变化、电容负载以及相邻线路间的耦合等。这些因素都可能导致时钟信号的不准确,对系统的稳定性和速度产生影响。

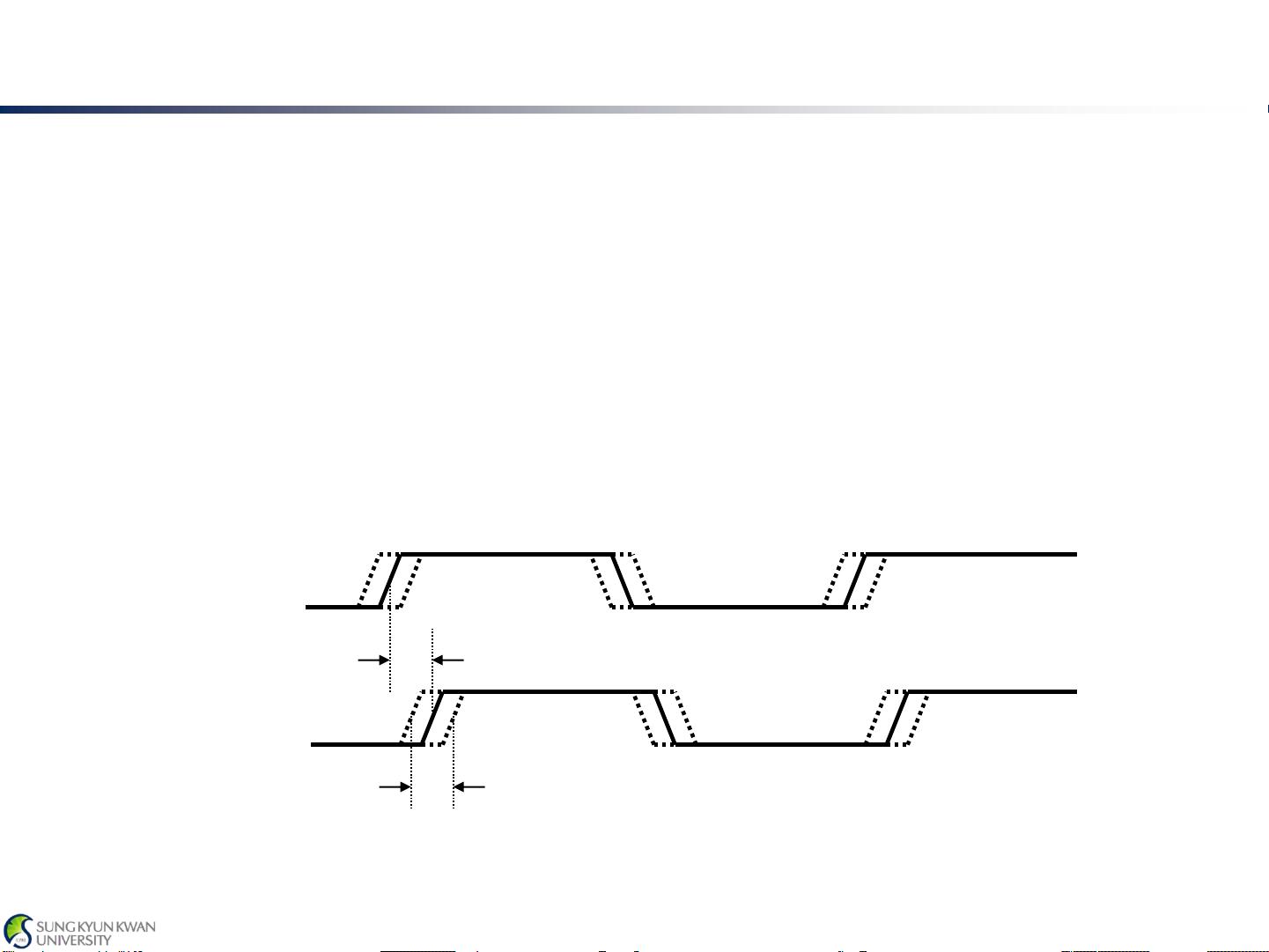

3. **时钟非理想性**:时钟非理想性主要表现为时钟偏斜(clock skew)和时钟抖动(clock jitter)。时钟偏斜是指同一个时钟信号到达不同位置的时间差,可能导致数据传递的不一致性;时钟抖动则是指时钟周期内连续边沿的随机变化,分为短期(cycle-to-cycle, tJS)和长期(long-term, tJL)两种,会影响有效周期时间和竞态条件(race condition)。

4. **时钟偏斜(Clock Skew)**:随着集成电路中寄存器数量的增加,时钟信号在传播过程中的延迟差异会增大。为了优化系统性能,通常需要插入延迟单元来减少这种延迟差异,确保所有寄存器在同一时刻被采样。

5. **时钟抖动(Clock Jitter)**:时钟抖动对高精度和高速数字系统的影响尤为显著,因为它直接影响到数据采样时刻的精确性。抖动可能会导致数据错误,降低系统工作频率,甚至导致系统崩溃。

6. **脉冲宽度变化(Duty Cycle Variation)**:对于水平敏感的时钟信号,时钟脉冲宽度的变化也需关注,因为它会改变有效的工作周期,可能影响系统的定时和稳定性。

7. **解决策略**:克服这些时序问题的方法包括优化时钟树结构以减小时钟偏斜,使用抖动抑制技术提高时钟质量,以及通过电源管理减少电源波动对时钟的影响。

通过对这些知识点的理解和掌握,工程师能够更好地设计和优化CMOS数字集成电路,确保其在各种环境和条件下都能稳定、高效地工作。

2017-11-24 上传

2022-06-17 上传

2023-07-14 上传

2021-10-06 上传

2021-10-02 上传

2010-09-26 上传

2011-05-27 上传

2014-02-15 上传

橙色半瓶水

- 粉丝: 134

- 资源: 14

最新资源

- VoIP服务器----Asterisk

- DIVCSS布局大全.pdf

- wxpython in action.pdf

- WEKA 3-5-3 Experimenter 指南

- Keil+winarm 编译环境设置及例程说明

- Marching Cubes算法

- mathematica教材

- STC12C2052AD芯片的AD转换程序

- SCA Java通用注解和API规范 SCA_JavaAnnotationsAndAPIsc_pub.pdf

- SCA 装配模型规范 SCA_AssemblyModel_V100c_pub.pdf

- OSWorkflow中文手册.pdfOSWorkflow中文手册.pdf

- Essential.Guide.to.Open.Source.Flash.Developmen

- 000-331 Testinside热门科目

- TCP/IP协议详解卷1_006(ICMP:Internet控制报文协议)

- Linux Programming by Example.pdf

- Excel2003函数应用完全手册