LATTICE时序约束深度解析:实现高性能FPGA设计

"LATTICE_非常详细的时序约束(中文教程)涵盖了FPGA设计中的重要概念和技术,旨在帮助设计者实现Timing Closure,确保系统性能达到预期的时序要求。教程详细介绍了从编码风格到综合约束,再到布局布线等各个阶段的关键步骤。

1. **Timing Closure的概念**:

Timing Closure是FPGA设计流程中的关键环节,随着现代FPGA设计的规模和复杂度增加,以及对系统性能的高要求,满足严格的时序目标变得越来越困难。设计者需要采用多种技术来提升系统性能,以确保设计满足时序约束。

2. **Timing Closure的步骤**:

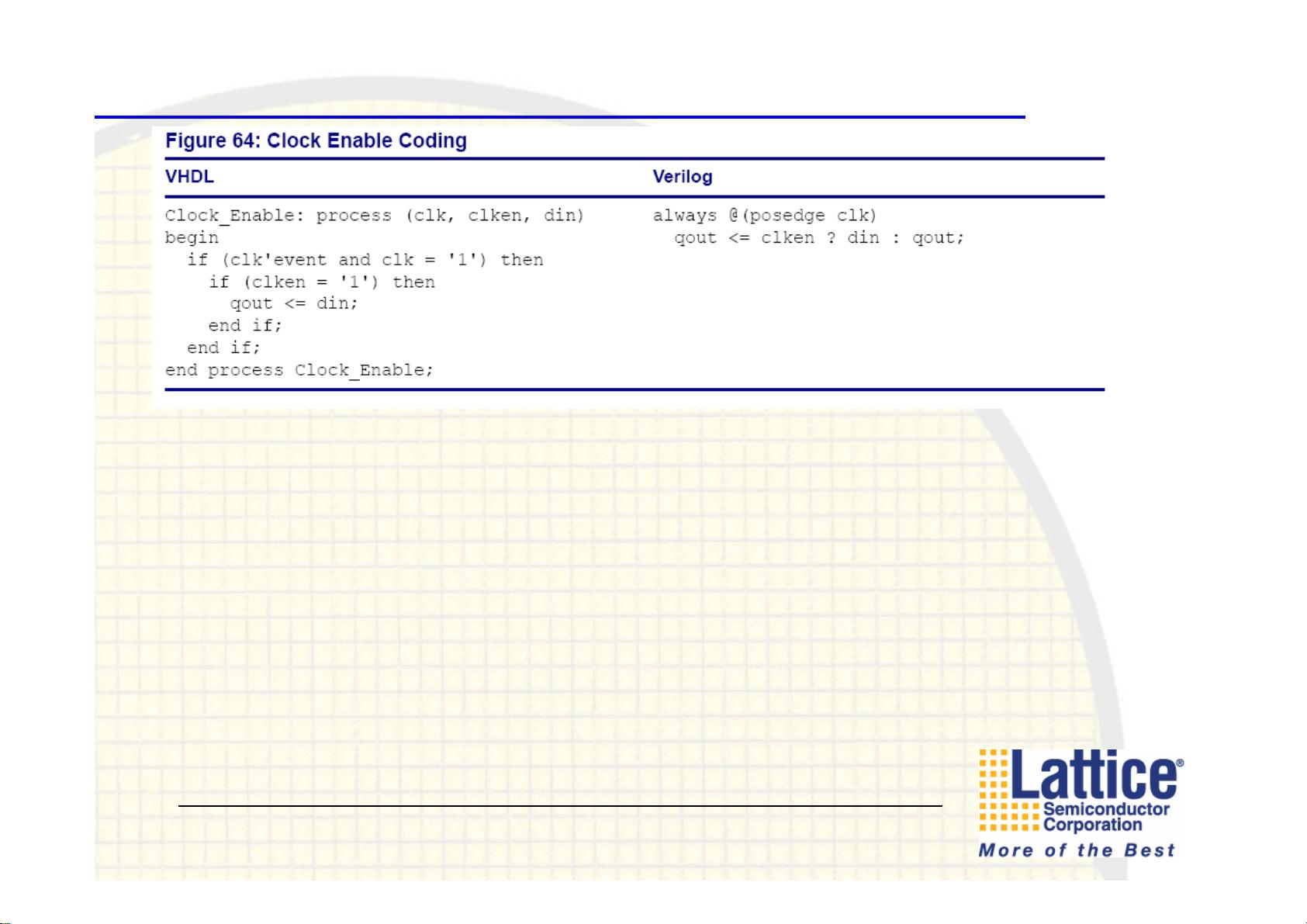

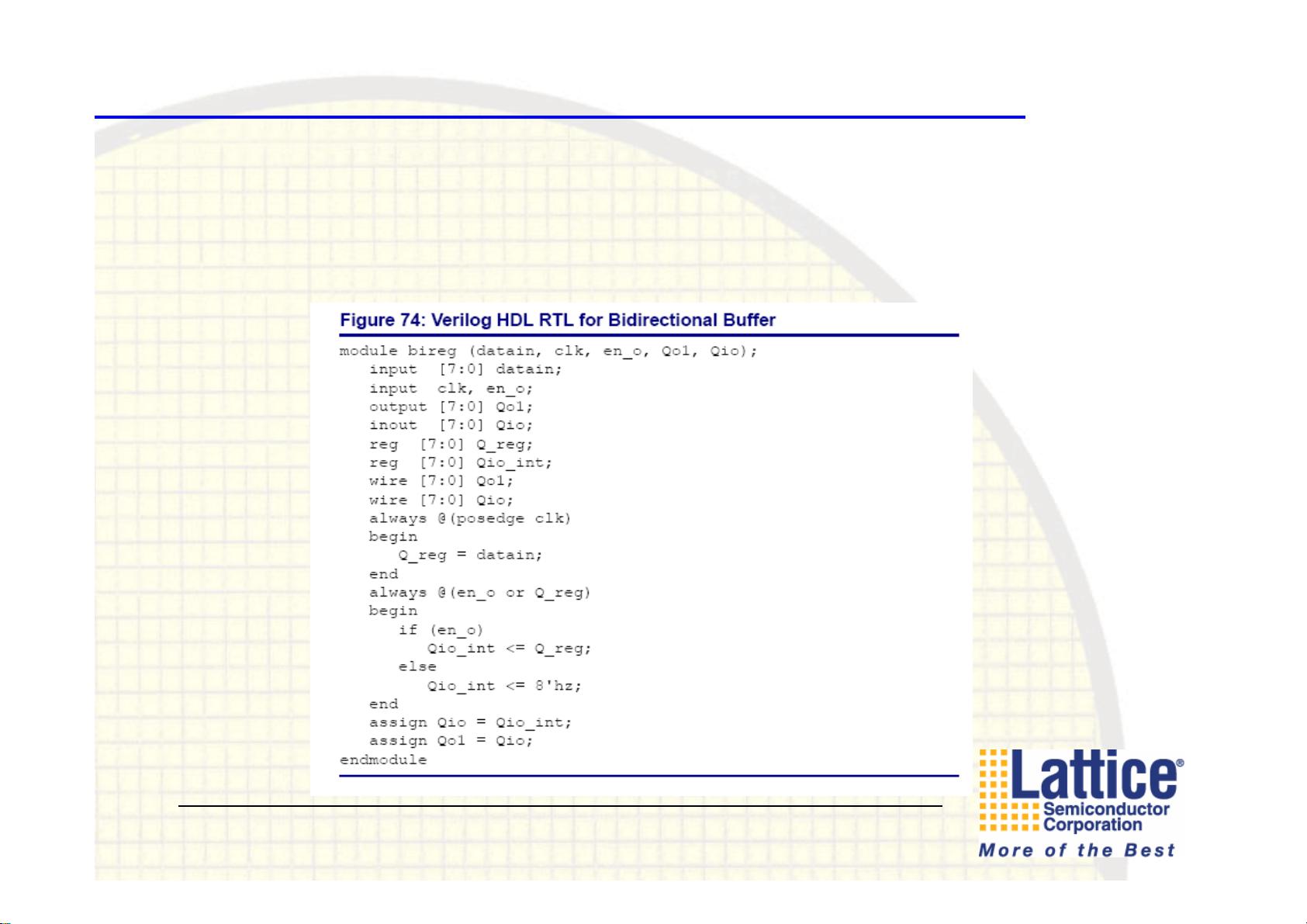

- **采用合适的Coding Style**:编码风格直接影响着设计的性能。例如,层次化编码(Hierarchical Coding)允许团队协作,加速设计和编译,并且关键模块的修改不会影响整体设计。

- **进行适当的综合约束**:通过设置综合规则,如限制逻辑深度、优化路径等,来优化设计的逻辑结构。

- **管脚锁定**:提前指定输入/输出引脚的位置,有助于提高时序性能和减少设计迭代次数。

- **实施Lattice约束**:Lattice特有的约束设置,确保工具能准确理解和应用设计规范。

- **Map**:逻辑映射阶段,将逻辑门级表示转换为设备特定的逻辑结构。

- **布局布线**:决定逻辑单元在FPGA内部的位置并连接它们,优化信号路径以满足时序要求。

- **控制Place and Route**:通过策略和指导原则,优化布局布线过程,以达到更好的时序性能。

- **Floorplanning设计**:预先规划FPGA内部的逻辑区域,有助于优化关键路径和降低时序风险。

3. **Coding Style**:

- **通用Coding Style**:包括层次化编码,使得设计更易于管理,多人协作更有效,同时也方便局部优化。

- **Team-Based设计**:多人协同工作,每个工程师可以专注于一部分设计,提高效率。

- **HierarchicalCoding**:分层设计有助于管理复杂性,允许独立优化关键模块。

教程通过深入讲解这些步骤和技巧,为FPGA设计者提供了实现高效时序约束的全面指南,以应对设计挑战,确保系统性能最大化。"

2022-09-22 上传

2023-10-11 上传

2022-07-15 上传

2022-09-22 上传

2021-09-29 上传

passionjjk

- 粉丝: 1

- 资源: 11

最新资源

- Postman安装与功能详解:适用于API测试与HTTP请求

- Dart打造简易Web服务器教程:simple-server-dart

- FFmpeg 4.4 快速搭建与环境变量配置教程

- 牛顿井在围棋中的应用:利用牛顿多项式求根技术

- SpringBoot结合MySQL实现MQTT消息持久化教程

- C语言实现水仙花数输出方法详解

- Avatar_Utils库1.0.10版本发布,Python开发者必备工具

- Python爬虫实现漫画榜单数据处理与可视化分析

- 解压缩教材程序文件的正确方法

- 快速搭建Spring Boot Web项目实战指南

- Avatar Utils 1.8.1 工具包的安装与使用指南

- GatewayWorker扩展包压缩文件的下载与使用指南

- 实现饮食目标的开源Visual Basic编码程序

- 打造个性化O'RLY动物封面生成器

- Avatar_Utils库打包文件安装与使用指南

- Python端口扫描工具的设计与实现要点解析