FPGA开发详解:异步 FIFO 控制与格雷码设计关键

需积分: 0 60 浏览量

更新于2024-08-03

收藏 29.18MB PDF 举报

FPGA开发汇总文档详细介绍了FPGA(Field-Programmable Gate Array)的异步设计中的关键要点,包括FPGA应用、数据结构设计、时钟同步以及地址控制机制。首先,异步设计中的FIFO(First-In-First-Out,先进先出)结构是常见应用,其特点是存储宽度一次处理的数据位数以及深度,这决定了数据的存储容量和读写速度。FIFO的可靠性和正确性在设计中尤为重要,例如通过读写指针的同步机制来判断状态,如empty和full。

1. 写入操作(write):写指针(wnptr)在写时钟(wr_clk)域内工作,当rd_ptr采集到写时钟并与wnptr比较后,如果读指针未到达,会生成一个信号撤销write_full。类似地,读取操作(read)通过rd_empty信号进行管理,当rdptr采集到读时钟并与wnptr比较,未达到写指针时,会撤销rd_empty。

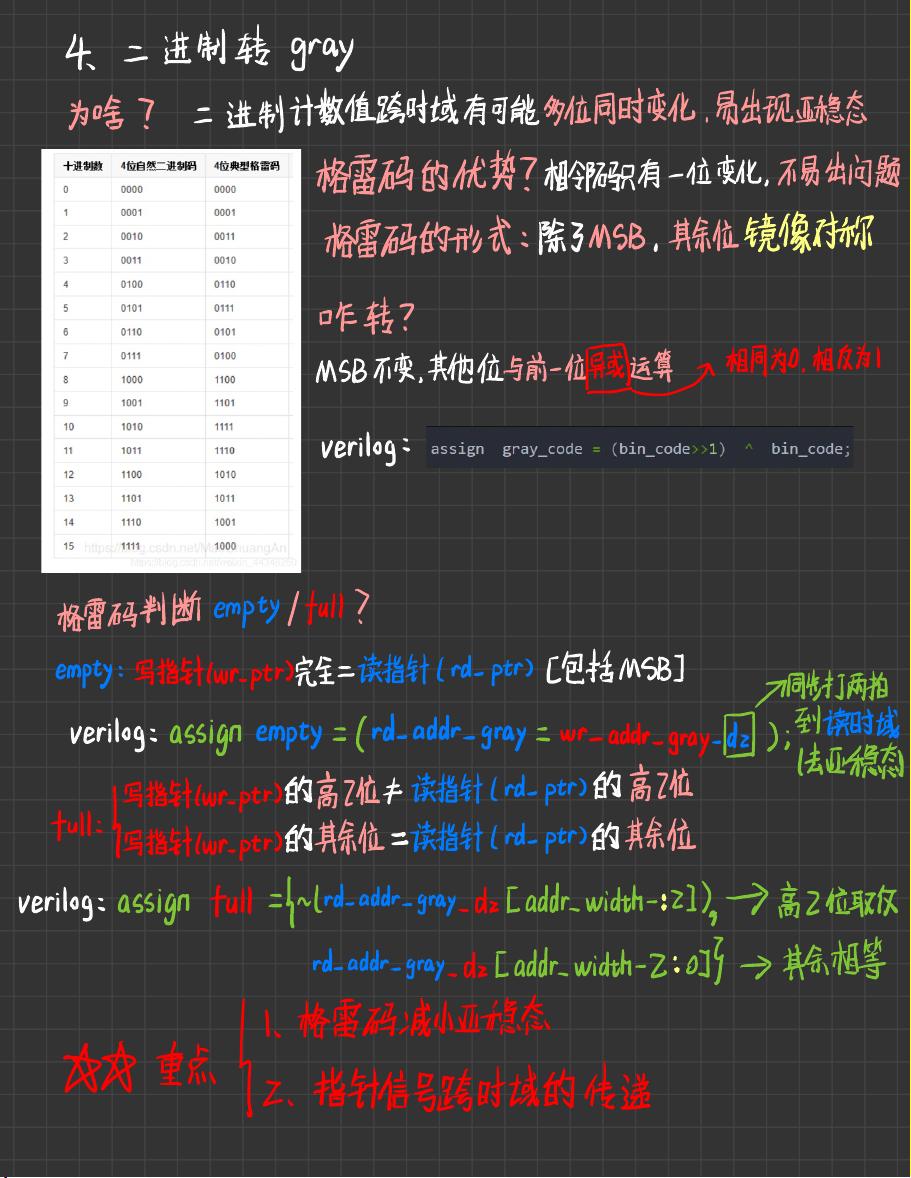

2. 地址控制:地址自增逻辑确保连续的数据访问,通过二进制编码转换为格雷码,避免跨时域计数值变化导致的亚稳态问题。格雷码的特点在于相邻码只有一个位置变化,这样能有效防止错误。转换方法是保持最高位不变,其他位与前一位按异或规则计算。

3. 时钟工作原理:读时钟和写时钟分别负责控制数据的读出和写入。它们在复位时都指向第一个单元,然后分别递增。empty和full状态的判断依赖于指针位置和深度,比如深度为2时,空状态的判断依据是读写指针的高位是否匹配。

4. 亚稳态和格雷码:在数据传输过程中,二进制计数可能同时改变多个位,导致亚稳态,而格雷码通过镜像对称和位运算避免了这种问题。在Verilog代码中,通过同步操作确保空闲和满的状态判断准确无误,通过高位同步和低位比较来减少亚稳态的影响。

FPGA开发中异步FIFO的设计需要精细的时钟控制、精确的地址管理和有效的亚稳态处理策略,以实现高效、稳定的数据流控制。这些知识点在实际的FPGA设计项目中至关重要,可以帮助工程师构建高性能的数字电路系统。

2023-04-04 上传

2022-04-22 上传

2022-04-22 上传

2023-04-04 上传

2022-11-16 上传

2022-04-22 上传

2022-04-22 上传

2019-09-30 上传

娃娃基

- 粉丝: 7

- 资源: 1

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用