RISC-V指令与控制器设计:RAM与ROM操作详解

需积分: 0 101 浏览量

更新于2024-08-05

收藏 854KB PDF 举报

实验5-指令读取和控制器设计1是一个旨在帮助学生深入理解计算机体系结构的关键课程,主要聚焦于RISC-V指令集架构。在这个实验中,参与者将学习并实践以下几个核心知识点:

1. **存储器理解**:

- 随机访问存储器(RAM)和只读存储器(ROM)是计算机内存的重要组成部分。RAM支持读写操作,常用于程序数据和变量存储,而ROM则只读,主要用于固化程序或配置信息。实验要求学生理解它们的工作原理,特别是数据位宽(如32位)和地址位宽(如最多24位)的概念。

2. **RISC-V指令集**:

- RISC-V是一种开放源代码指令集架构,实验关注的是RV32I指令集,包括R型(算术逻辑运算)、I型(立即数操作)、U型(无条件转移)和S型(系统调用)指令。学生需要熟悉这些指令的类型和格式,以便在控制器设计中正确处理。

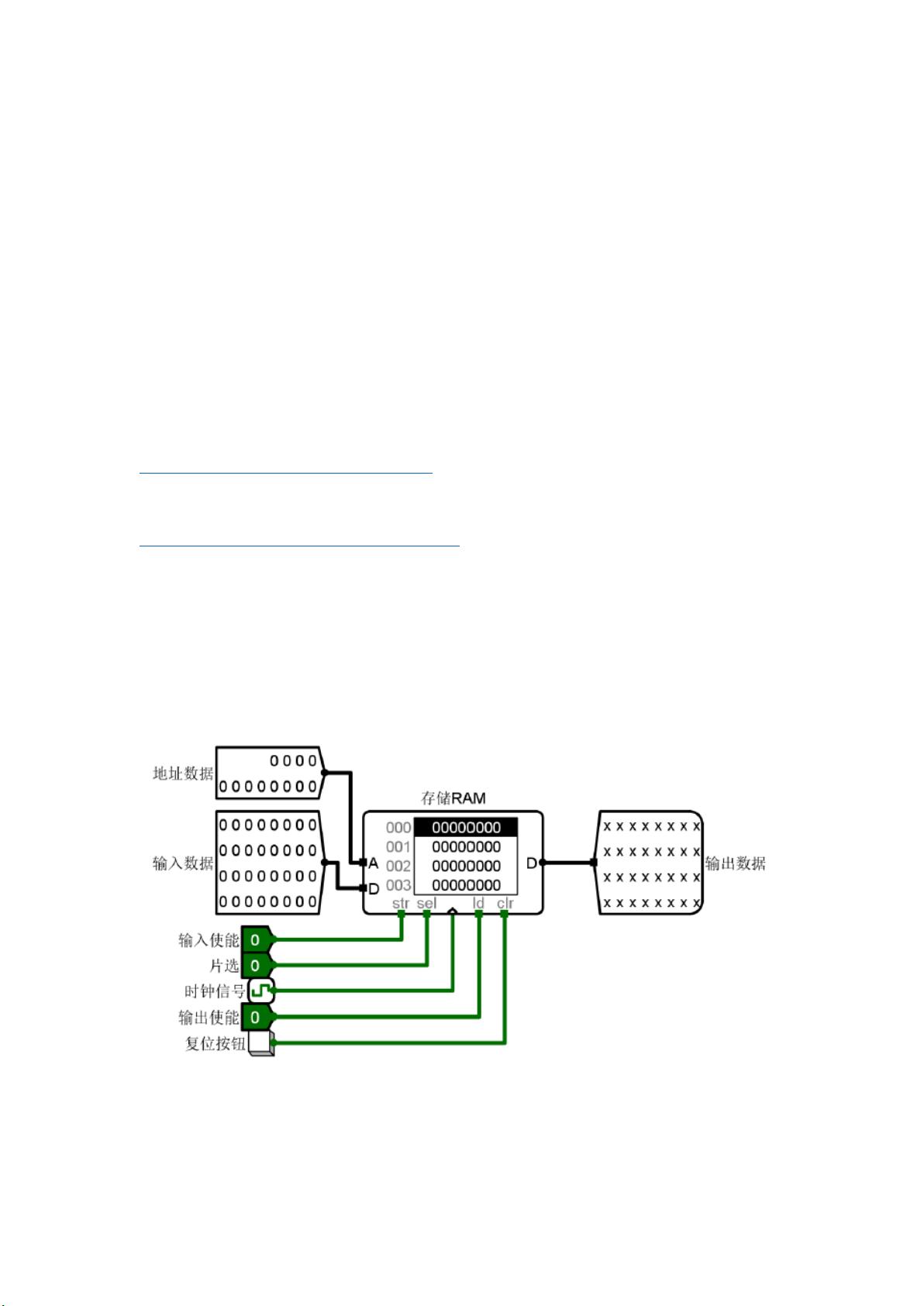

3. **Logisim软件应用**:

- Logisim是一款开源的逻辑仿真软件,用于设计和验证数字电路。在这个实验中,学生将学习如何利用Logisim来实现指令的取指(fetching instructions)、指令解析(decoding),以及对立即数扩展和操作数存取的操作。通过分离的加载和存储引脚模式,学生将实践如何配置RAM以实现数据的存取。

4. **硬件实现步骤**:

- 实验中具体操作包括设置RAM组件的地址位宽(如12位)和数据接口模式,以及使用Logisim十六进制编辑器进行数据输入和存储。实验还要求学生通过观察测试部分的输出验证RAM功能的正确性,包括写入和读取操作的顺序。

5. **指令执行流程**:

- 学生将实际构建一个控制器,模拟9条RISC-V指令的执行过程,包括数据处理、指令调度和控制信号的生成,这有助于加深对指令执行机制的理解。

通过这个实验,学生不仅能够提升对底层硬件的理解,还能锻炼逻辑设计和编程能力,为后续的计算机系统设计打下坚实基础。

2009-12-10 上传

2022-07-03 上传

2023-10-31 上传

2009-04-18 上传

2022-06-20 上传

2022-01-06 上传

2024-05-29 上传

2024-05-12 上传

2012-01-09 上传

乔木Leo

- 粉丝: 31

- 资源: 301

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新

已收录资源合集

已收录资源合集