使用ISE13.1编译FPGA工程及下载到basys2开发板教程

"ISE13.1教程"

Xilinx ISE(Integrated Software Environment)13.1 是一个集成设计环境,用于开发基于Xilinx FPGA(Field-Programmable Gate Array)的电子系统。这个教程详细讲解了如何使用ISE 13.1版本来创建一个新的FPGA工程,从建立项目到最终下载配置文件到硬件开发板——Basys2的过程。

1. **新建工程**

新建工程是设计流程的第一步。在ISE中,通过“File”菜单选择“New Project”,指定工程名称和存储位置。接着,你需要在“Family”、“Device”、“Package”和“Speed Grade”字段中选择对应的FPGA器件参数。完成这些设置后,点击“Finish”,你会在工作区看到新建的工程。

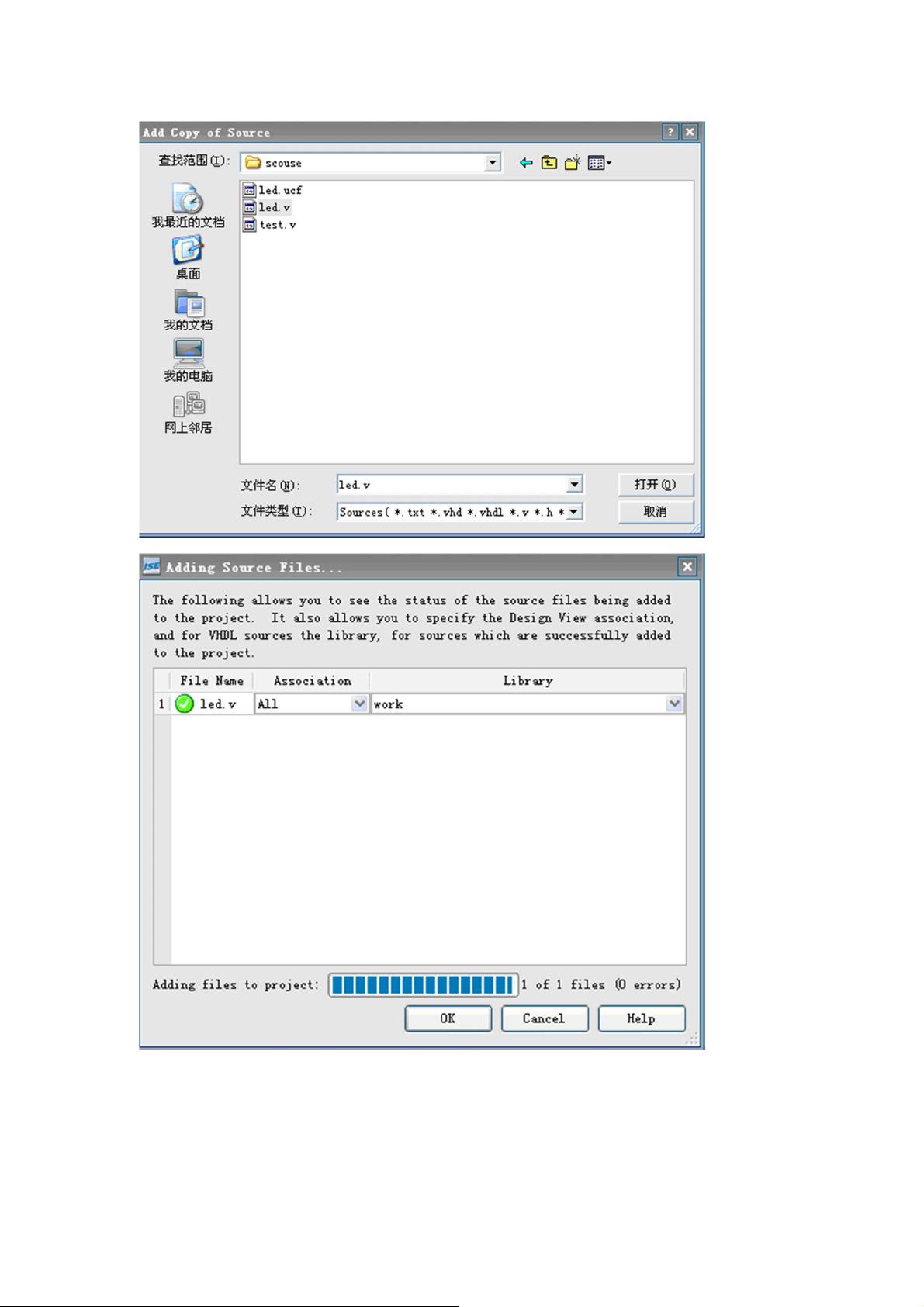

2. **添加源文件**

右键点击工程文件夹,选择“Add/Remove Sources”来添加Verilog或VHDL源文件。你可以直接添加现有文件,或者通过“New Source”创建新文件。添加后,源文件会在工作区中显示。

3. **综合**

在Hierarchy窗口中选中设计模块,然后在Processes窗口中双击“Check Syntax”检查源代码是否有语法错误。无误后,进行“Synthesize - XST”操作,进行综合步骤,将高级语言描述转换为逻辑门级网表。

4. **仿真**

仿真允许你在下载到硬件之前预览设计行为。通过“Add/Remove Sources”添加测试平台文件(如test.v),然后运行“Simulate Behavioral Model”。在Isim仿真环境中,可以观测信号的变化,模拟设计的运行。

5. **添加用户约束**

用户约束文件(UCF)用于指定输入/输出端口的物理特性,如IOBank分配、时钟约束等。通过“Add/Remove Sources”添加UCF文件,确保设计符合硬件的要求。

6. **布局布线**

综合后的设计需要经过“Implement Design”进行布局和布线,这个过程将逻辑网表转化为物理实现,确定FPGA内部资源的分配和互连。

7. **配置文件生成**

完成布局布线后,双击“Generate Programming File”生成.bit文件,这是可以直接加载到FPGA上的配置数据。

8. **下载到硬件**

将Basys2开发板连接到电脑,关闭SW0开关。启动Digilent Adept软件,它会自动检测开发板。选择生成的.bit文件进行编程,确认操作后,软件将把配置数据下载到FPGA中。当下载成功,开发板上的LED将按照设计预期点亮。

这个教程涵盖了从头到尾的FPGA设计流程,对于初学者来说是一份非常实用的指南,帮助他们理解ISE工具的使用以及FPGA设计的基本步骤。

1596 浏览量

205 浏览量

104 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

179 浏览量

zl201110

- 粉丝: 56

最新资源

- GNU链接器ld使用指南

- 精通GNU工具集:Autoconf、Automake与autotools详解

- 构建自己的网络安全实验室:网络测试实战指南

- SQLServer学生信息管理系统设计:需求分析与实体关系

- 开关电源设计关键因素分析

- 面向对象应用软件系统框架设计与实践

- 快速入门UCOS-II:在PC上搭建与运行示例

- 非线性滤波器设计优化方法

- 最优滤波理论专著:数据压缩与通信系统的关键

- 操作系统详解:管理与控制计算机资源

- C语言在嵌入式系统编程中的应用与技巧

- 高阶Perl:编程思维革命的经典之作

- 微波技术实验教程:从理论到实践

- JavaFX:打造丰富的移动应用程序

- GNUmake中文手册:构建与理解

- JavaFX技术深度探索:控件与布局指南