Verilog实现同步状态机:原理与设计实例

需积分: 10 120 浏览量

更新于2024-08-01

收藏 233KB PDF 举报

"该文主要介绍了Verilog语言中同步状态机的设计原理和实现方法,包括同步状态机的结构、类型以及常见的描述风格,并通过两个具体的例子进行详细解释。"

同步状态机是数字系统设计中的重要组成部分,常用于控制逻辑和序列处理。在Verilog中,我们可以使用硬件描述语言来构建同步状态机。同步状态机的关键特点是状态的改变只发生在时钟边沿,通常为正跳变,这保证了系统在时钟周期内的稳定性和可预测性。

状态机的核心是状态记忆部件,通常采用D触发器来存储当前状态。D触发器在正跳变沿采样输入,确保在时钟上升沿到来时,状态的更新同步进行。如果一个状态机使用n个触发器,那么它最多可以表示2^n个不同的状态。

根据输出与输入的关系,同步状态机主要分为两类:Mealy型和Moore型。Mealy型状态机的输出不仅取决于当前状态,还依赖于当前的输入,而Moore型状态机的输出只与当前状态有关,不随输入变化而即时改变。在实际应用中,Mealy型状态机更为常见。

同步状态机的实现方式多样,常见的有以下几种:

1. 二进制码表示状态:每个状态用一个唯一的二进制编码表示。

2. 格雷码表示状态:这种编码方式减少了相邻状态间的转换误差。

3. 独热码表示状态:每个状态只有一个位为1,其余位为0,这种方式有利于检测非法状态。

在Verilog中,状态机的描述通常使用`always`语句块,根据设计需求可以选择不同的风格,如Onealways、Twoalways或Threealways风格。这些风格主要区别在于如何分配时钟、复位和状态更新的逻辑。

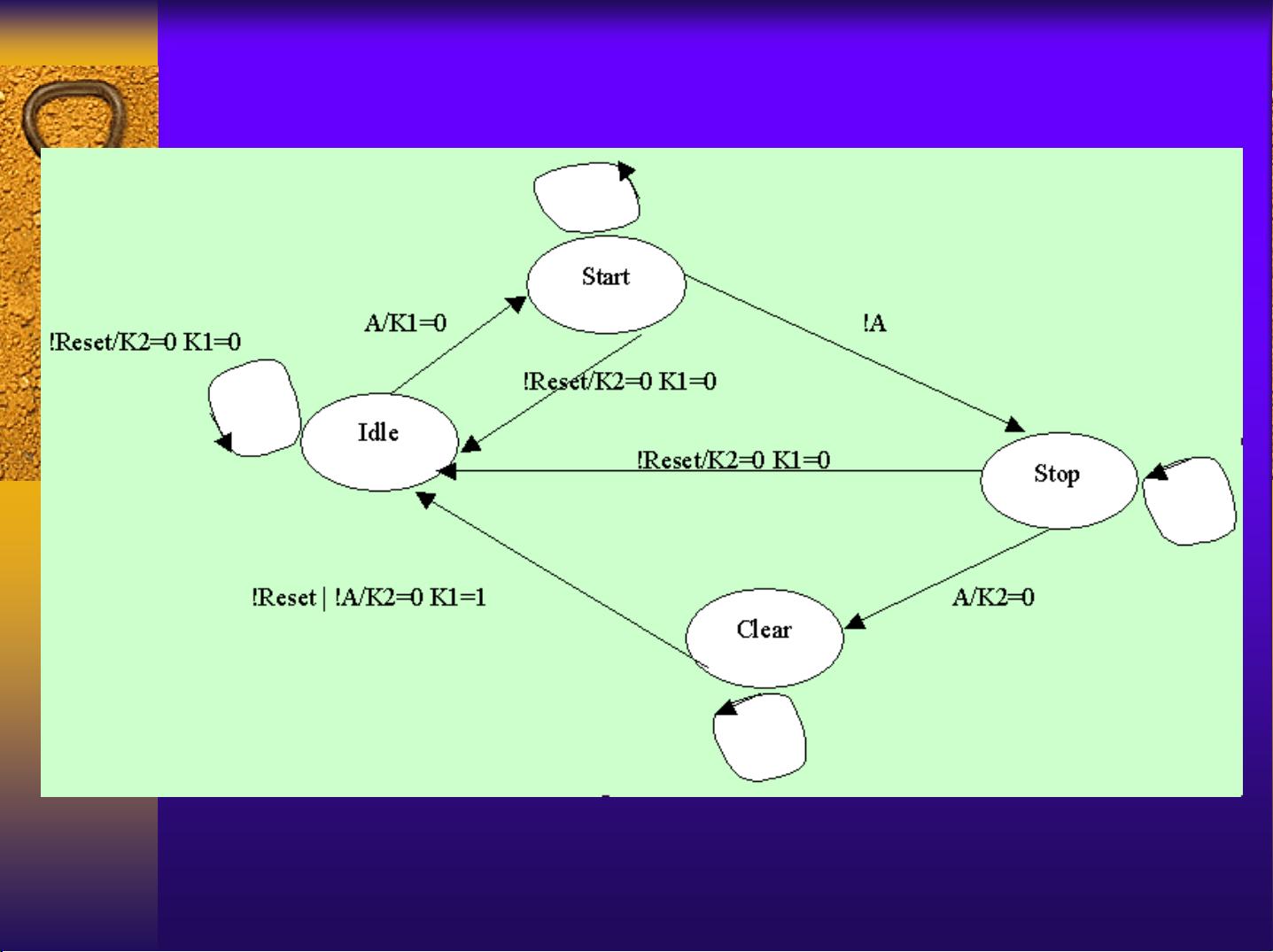

例如,例9.1展示了一个用可综合Verilog代码实现的同步状态机,其中`state`变量用于存储状态,`idle`、`start`、`stop`和`clear`是预定义的参数,表示不同的状态。在时钟正跳变沿,状态根据`case`语句进行更新,同时输出`k2`和`k1`的值根据当前状态决定。这个状态机是Mealy型,因为输出`k1`和`k2`的值不仅与当前状态有关,也受输入`a`的影响。

另一个例子9.2则展示了使用独热码表示状态的情况,虽然具体内容没有给出,但可以推测其设计将使用多个`reg`变量来表示每个可能状态的激活状态。

同步状态机在Verilog中通过状态寄存器和逻辑判断实现,可以灵活地设计为Mealy型或Moore型,并且可以通过多种编码方式表示状态。理解和掌握同步状态机的设计原则和实现方法对于进行数字系统设计至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-24 上传

点击了解资源详情

2023-04-23 上传

2023-11-08 上传

2021-10-01 上传

2010-04-04 上传

ai1013547

- 粉丝: 2

- 资源: 21

最新资源

- mattgirdler.github.io

- cloudinary_public:Dart包装器,可将媒体文件上传到cloudinary

- ulabel:基于浏览器的图像批注工具

- lickwolf.github.io

- .NET在线二手交易系统的ASP毕业设计(源代码+论文).zip

- mern-react:使用Javascript创建Staycation前端(ReactJS)

- Accuinsight-1.0.24-py2.py3-none-any.whl.zip

- js-algorithms:各种算法的 JavaScript 实现

- WebCursos

- workers-forms

- ajalabs_placeholder:AJAlabs.com当前的占位符网站

- 基于web的实验室管理系统毕业设计(自动排课功能的实现).zip

- fbfgbfqq

- 博客

- Qt6可进行录像录音代码特性

- voxel_survival