FPGA设计基础:DFF与D-Latch解析及时间模型

需积分: 9 175 浏览量

更新于2024-09-12

收藏 899KB DOC 举报

"FPGA设计基础,探讨了D型触发器(DFF)和D-Latch的基本原理,以及寄存器的时序概念,包括建立时间、保持时间和亚稳态等关键时间模型。"

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,广泛用于数字电路设计中。在FPGA设计中,了解和掌握基本的寄存器时序至关重要。D型触发器(DFF)和D-Latch是两种常用的数据存储单元,它们在时钟信号的控制下存储和传递数据。

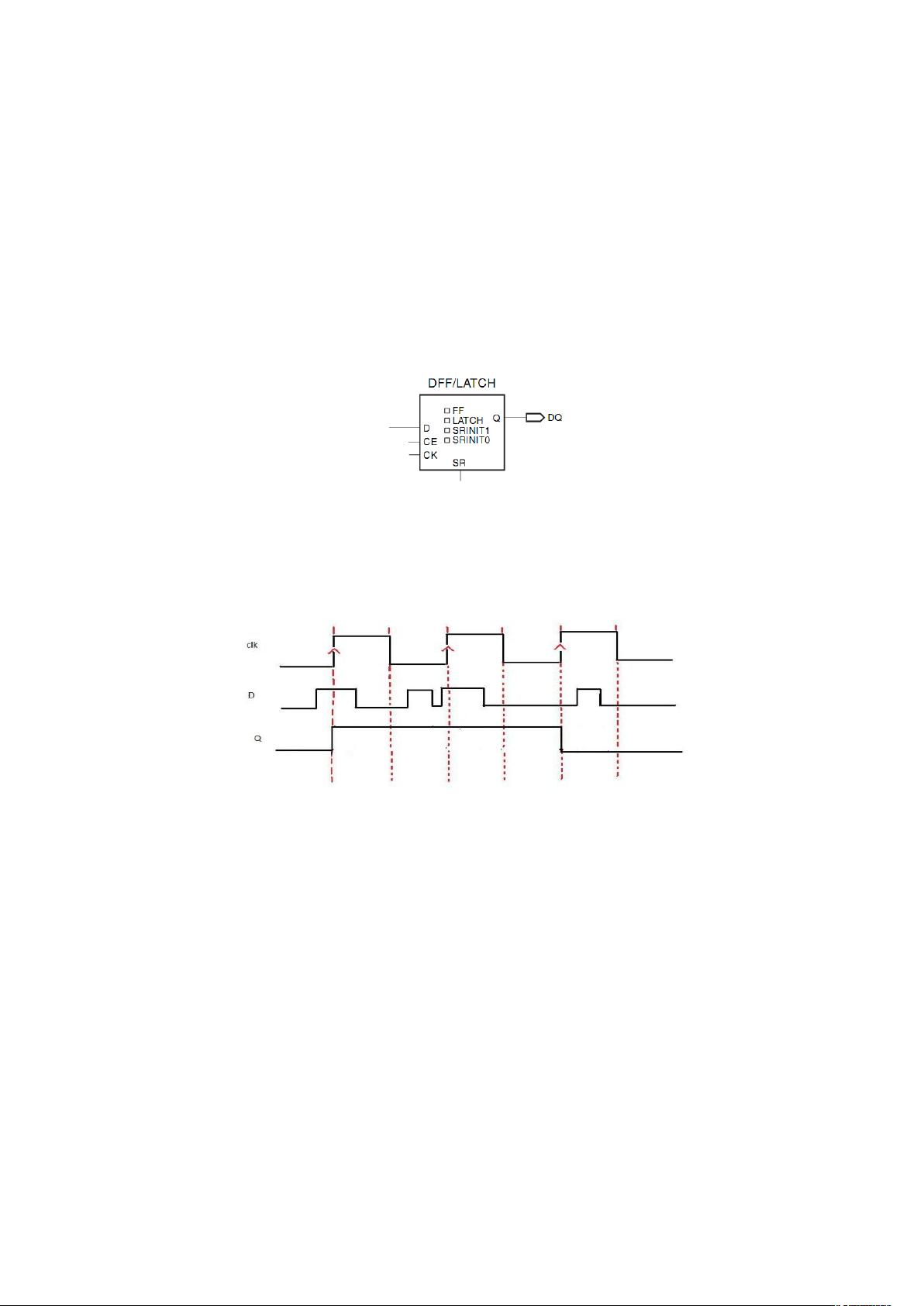

D型触发器(DFF)具有四个输入:D(数据输入)、CE(时钟使能)、CK(时钟)和SR(置位/复位),一个输出DQ。当CE为有效状态时,DFF会在CK的上升沿或下降沿捕获D输入的数据,并将其保持到下一个时钟沿。这意味着,即使在D输入改变,DQ输出也会保持不变,除非时钟边沿到来。

D-Latch则在CE为高电平时对D输入进行采样,并在CE变为低电平时锁存数据。与DFF不同,D-Latch在时钟为高电平的整个期间,输入数据的任何变化都会立即反映在输出DQ上。DFF是沿触发,而D-Latch是电平触发,这决定了它们在不同应用场景中的选择。

在FPGA设计中,建立时间(setup time)和保持时间(hold time)是确保正确数据传输的关键。建立时间是指在时钟上升沿到来前,数据必须保持稳定的时间,以确保数据能够被正确地打入触发器。而保持时间则是时钟上升沿后,数据仍需保持不变的最小时间,以避免数据丢失。如果这两个时间条件不满足,可能会导致数据错误。

亚稳态(metastability)是时序违例的一种表现,它发生在数据传输过程中,如数据输入未满足建立时间或保持时间,或复位信号释放不满足恢复时间要求时。在这种情况下,触发器输出会经历一段不确定的时间,即决断时间(resolution time),在这段时间内,输出会在0和1之间振荡,最终随机稳定在0或1。亚稳态是设计中的潜在风险,需要通过良好的时序约束和设计策略来避免。

理解并掌握这些基础知识对于进行高效且可靠的FPGA设计是至关重要的。设计师必须确保所有时序路径满足严格的时序约束,以防止亚稳态和其他潜在问题,从而保证系统的稳定性和可靠性。在实际设计中,通常会使用高级的综合工具和时序分析工具来辅助优化和验证设计,以确保满足这些时序要求。

2010-12-01 上传

2009-08-25 上传

2007-09-30 上传

2019-09-08 上传

2014-04-13 上传

troes

- 粉丝: 0

- 资源: 2

最新资源

- Python中快速友好的MessagePack序列化库msgspec

- 大学生社团管理系统设计与实现

- 基于Netbeans和JavaFX的宿舍管理系统开发与实践

- NodeJS打造Discord机器人:kazzcord功能全解析

- 小学教学与管理一体化:校务管理系统v***

- AppDeploy neXtGen:无需代理的Windows AD集成软件自动分发

- 基于SSM和JSP技术的网上商城系统开发

- 探索ANOIRA16的GitHub托管测试网站之路

- 语音性别识别:机器学习模型的精确度提升策略

- 利用MATLAB代码让古董486电脑焕发新生

- Erlang VM上的分布式生命游戏实现与Elixir设计

- 一键下载管理 - Go to Downloads-crx插件

- Java SSM框架开发的客户关系管理系统

- 使用SQL数据库和Django开发应用程序指南

- Spring Security实战指南:详细示例与应用

- Quarkus项目测试展示柜:Cucumber与FitNesse实践