Cortex-M3+技术参考手册:处理器架构与编程指南

需积分: 48 143 浏览量

更新于2024-07-28

收藏 1.67MB PDF 举报

"Cortex-M3+技术参考手册是一本针对Cortex-M3处理器的详细工具书,旨在帮助开发者在编写代码时进行查阅。手册涵盖了处理器的组件、编程模型、系统控制、存储器映射以及异常处理等多个核心主题。"

在Cortex-M3处理器中,有几个关键组件和特性:

1. **处理器内核**: Cortex-M3基于ARMv7-M架构,是一个高效能、低功耗的微控制器核心,支持Thumb2指令集。

2. **Nested Vector Interrupt Controller (NVIC)**: NVIC是处理器的中断控制器,它负责管理中断请求的优先级和向量处理。

3. **Bus Matrix**: 这是处理器内部的总线结构,用于连接各个组件并管理数据传输。

4. **Fault Handling**: 包括Fault Handling Block (FPB)、Data Watchpoint and Trace (DWT)、Instrumented Trace Macrocell (ITM)等,这些组件支持故障处理和调试功能。

5. **Memory Protection Unit (MPU)**: 提供了内存区域的保护,确保代码和数据的安全性。

6. **Embedded Trace Macrocell (ETM)** 和 **Trace Port Interface Unit (TPIU)**: 支持实时调试和性能分析。

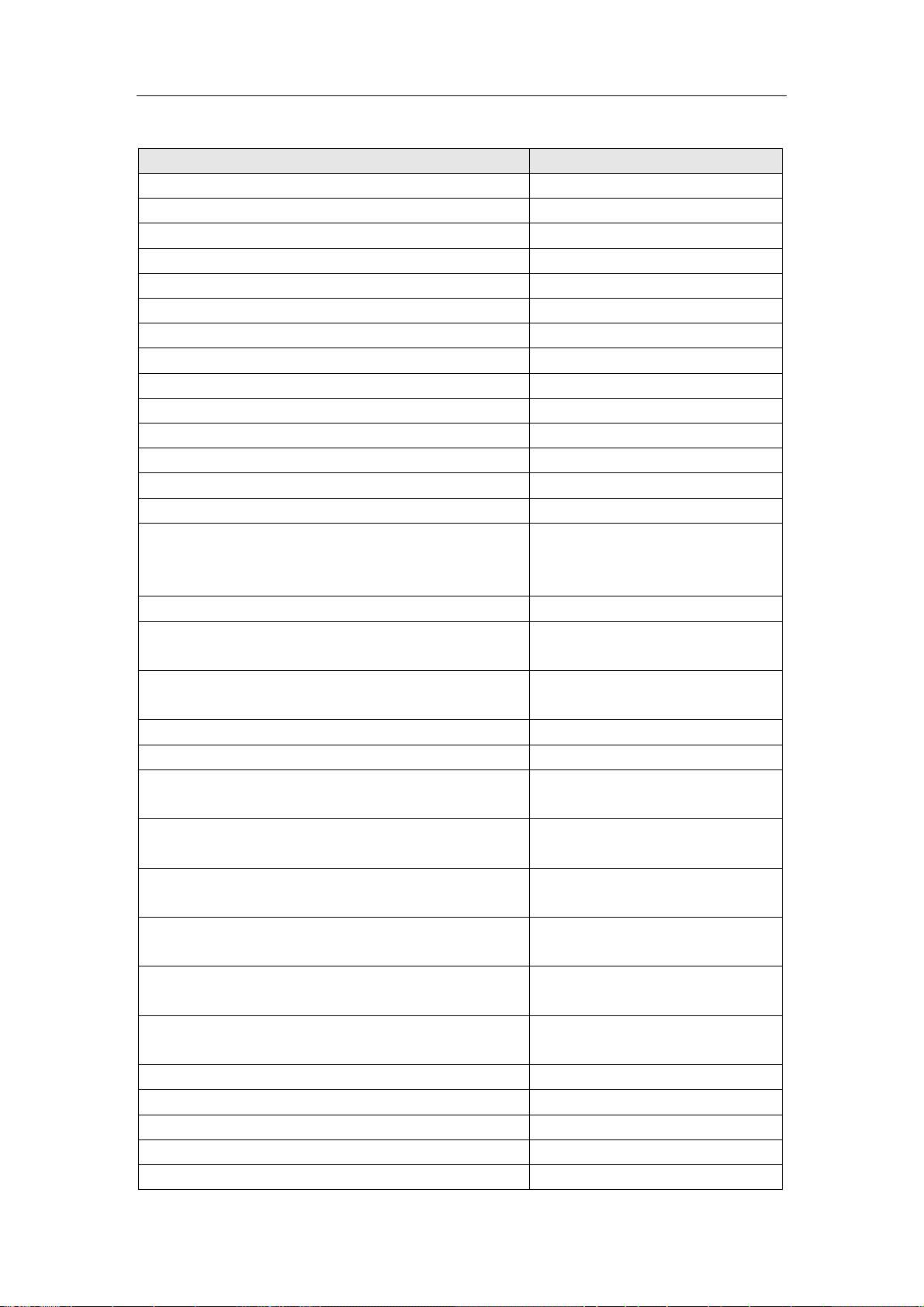

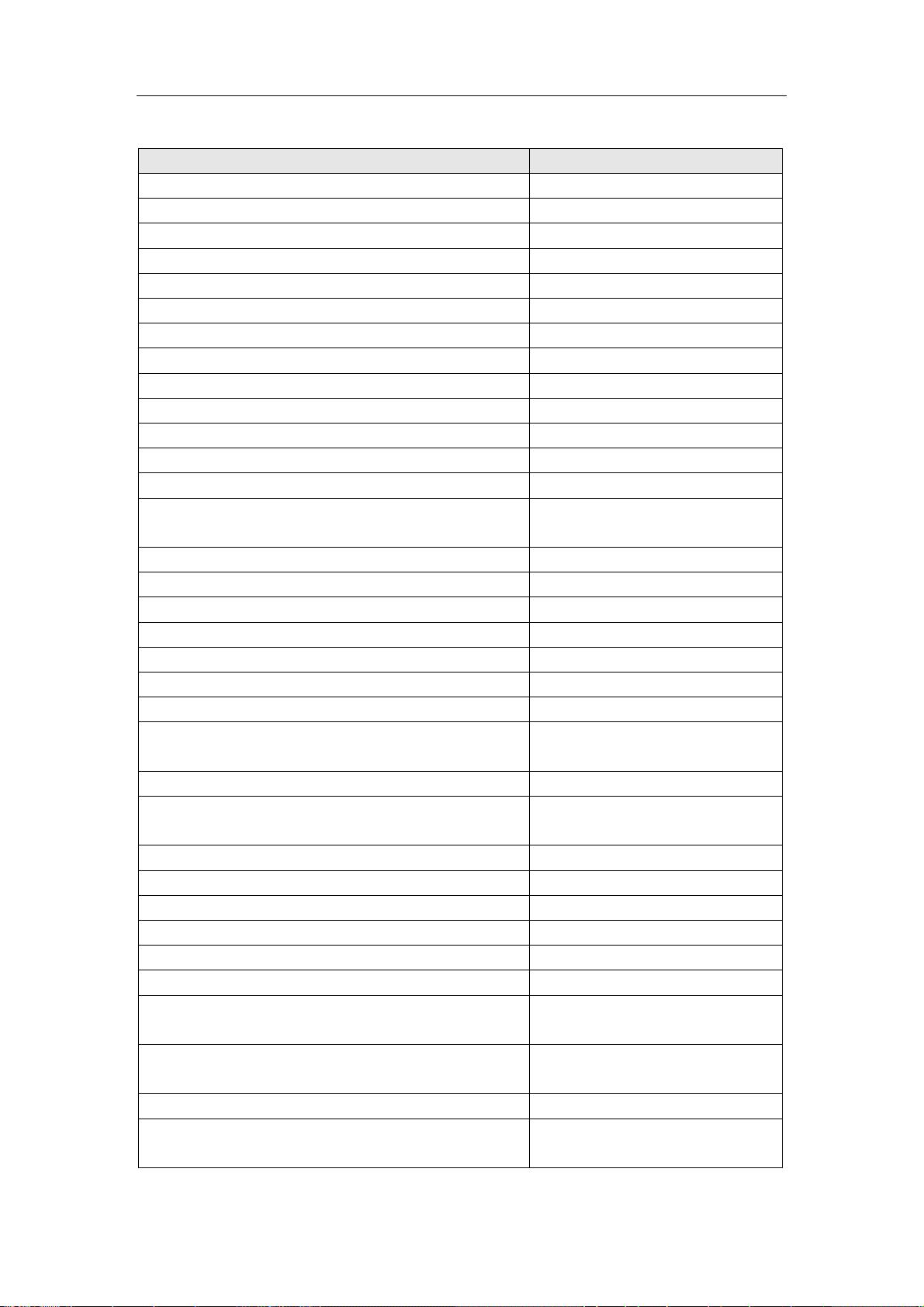

7. **System Control**: 包含一系列的寄存器,如NVIC、调试寄存器等,用于系统级别的配置和控制。

编程模型部分介绍了:

1. **工作模式和状态**: 包括特权模式和用户模式,以及运行状态的切换。

2. **寄存器结构**: 包括13个通用寄存器(R0-R12)、3个状态寄存器(SP、LR和PC),以及一个扩展的程序状态寄存器(xPSR)。

3. **数据类型和存储器格式**: 描述了处理器支持的数据类型,以及内存的组织方式。

4. **指令集**: Cortex-M3支持的Thumb2指令集提供了高效的16位和32位指令。

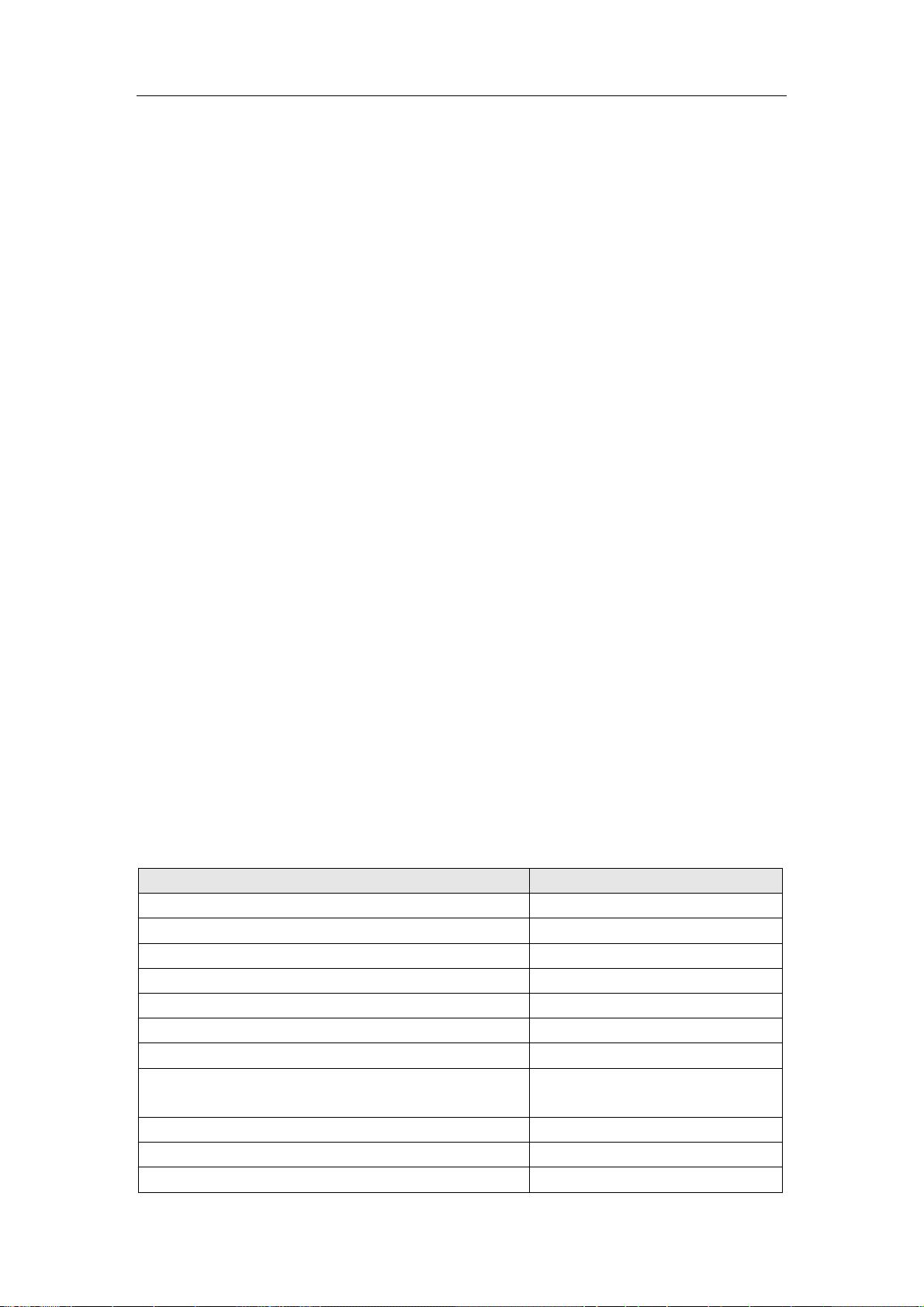

系统控制章节详细列出了处理器中的各种寄存器,包括NVIC、调试接口、存储器保护单元等的寄存器配置。

存储器映射部分涉及:

1. **Bit-banding**: 提供了一种高效的位操作方法,使得对内存中的单位进行访问变得更加简单。

2. **ROM存储器表**: 用于初始化和固件更新。

异常处理部分讲解了:

1. **异常模型**: 异常可以是中断或硬件错误,它们中断正常执行流程并跳转到相应的处理程序。

2. **异常类型**: 包括复位、中断、系统调用等。

3. **优先级和抢占**: 异常的优先级可以被配置,并支持抢占机制。

4. **异常退出和处理器返回**: 描述了如何从异常处理程序返回到正常程序执行。

Cortex-M3+技术参考手册为开发者提供了全面的技术细节,是理解和利用Cortex-M3处理器进行嵌入式系统开发的重要参考资料。

398 浏览量

2014-06-21 上传

179 浏览量

2022-08-04 上传

2021-11-27 上传

2022-03-15 上传

2009-03-03 上传

lwp1904

- 粉丝: 1

- 资源: 79

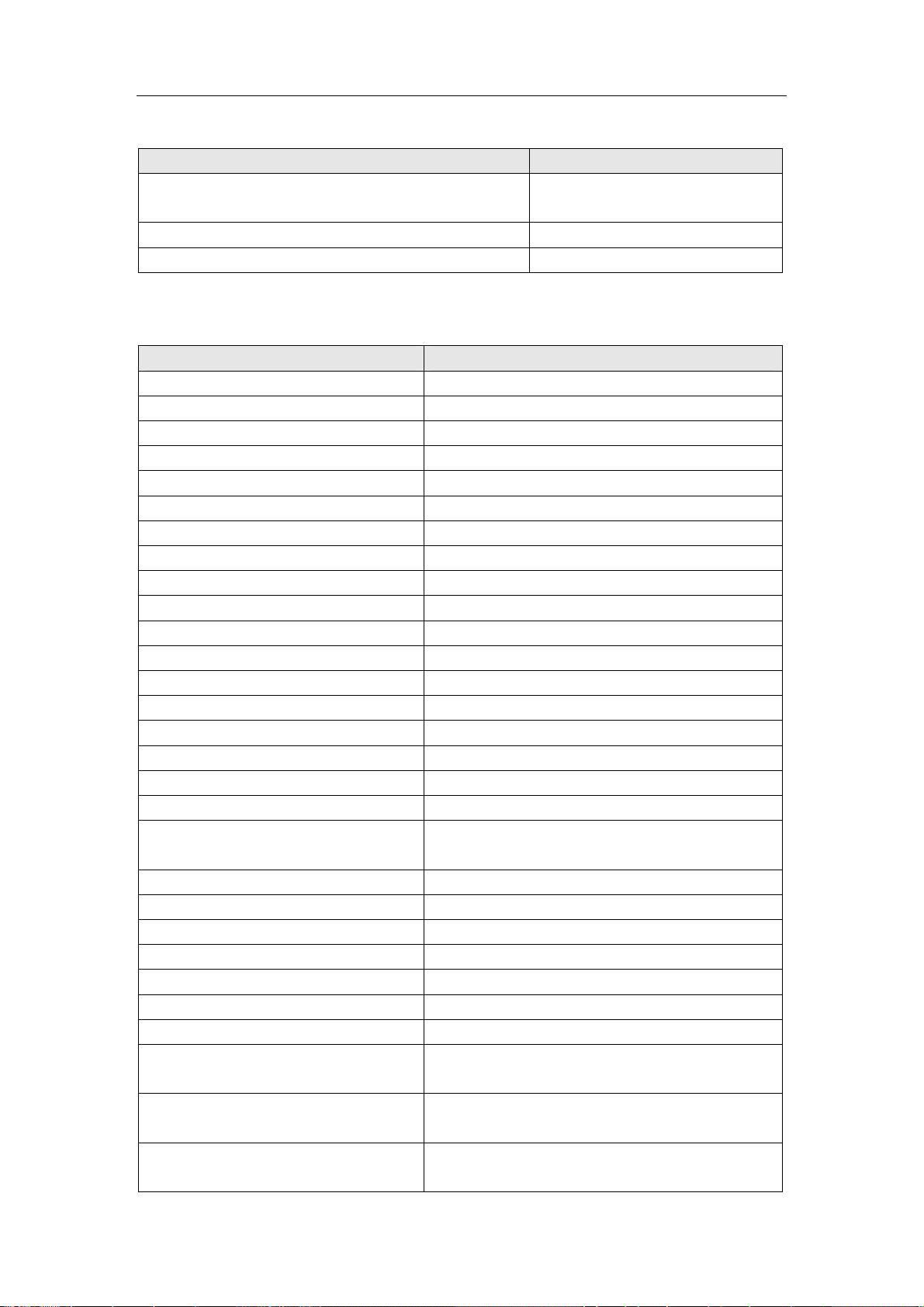

最新资源

- waterGame

- angular-trianglify-animate:Angular Trianglify Animate 是一个很小的 (2kb) 插件,用于为您的页面添加对图像 SVG 动画的支持

- malg-cheong:부산대

- CSE316

- 2ALIENTEK 产品资料.rar

- 艾蒙坎

- 2020policebrutality:2020年警察暴行数据的Web界面

- 高端的婚纱摄影前端网页模板.zip

- idea-prado-plugin:PRADO框架对IntelliJ IDEAPHPStorm的支持

- RF++-开源

- show-action-sheet.zip

- 词法分析 编译原理实验/课程设计(C++实现)

- 影刀RPA系列公开课6:内容简介.rar

- 零基础入门CV数据集-数据集

- elec-market:电力批发市场的典范

- demo_spring_security.zip