DS/FH混合扩频接收机解扩及同步FPGA实现

100 浏览量

更新于2024-08-30

收藏 123KB PDF 举报

"DS/FH混合扩频接收机的解扩及同步技术通过FPGA实现,采用ALTERA公司的APEX20K200RC240-1 FPGA芯片和Quartus II开发平台。文章重点阐述了解扩模块的设计,包括数字下变频器、NCO、码发生器、相关累加器和伪码移相电路的FPGA实现。NCO通过相位累加器和查找表产生精确时钟,控制码发生器,实现信号捕获和跟踪。"

DS/FH混合扩频通信系统结合了直接序列(DS)和跳频(FH)两种扩频方式,提高通信的安全性和抗干扰能力。在接收端,解扩及同步是至关重要的环节,它涉及到数字下变频、相关运算以及时钟同步等多个步骤。传统的实现方式通常依赖于多个专用芯片,这不仅增加了系统的复杂性,还限制了小型化和集成化的发展。

FPGA(Field-Programmable Gate Array)作为一种可编程逻辑器件,允许设计者在单个芯片上集成多种功能,极大地简化了硬件设计。在本文中,设计者使用ALTERA的APEX20K200RC240-1 FPGA芯片,配合Quartus II开发工具,实现了混合扩频接收机的解扩和同步核心模块,降低了硬件成本,提高了系统集成度。

解扩模块的核心组成部分包括:

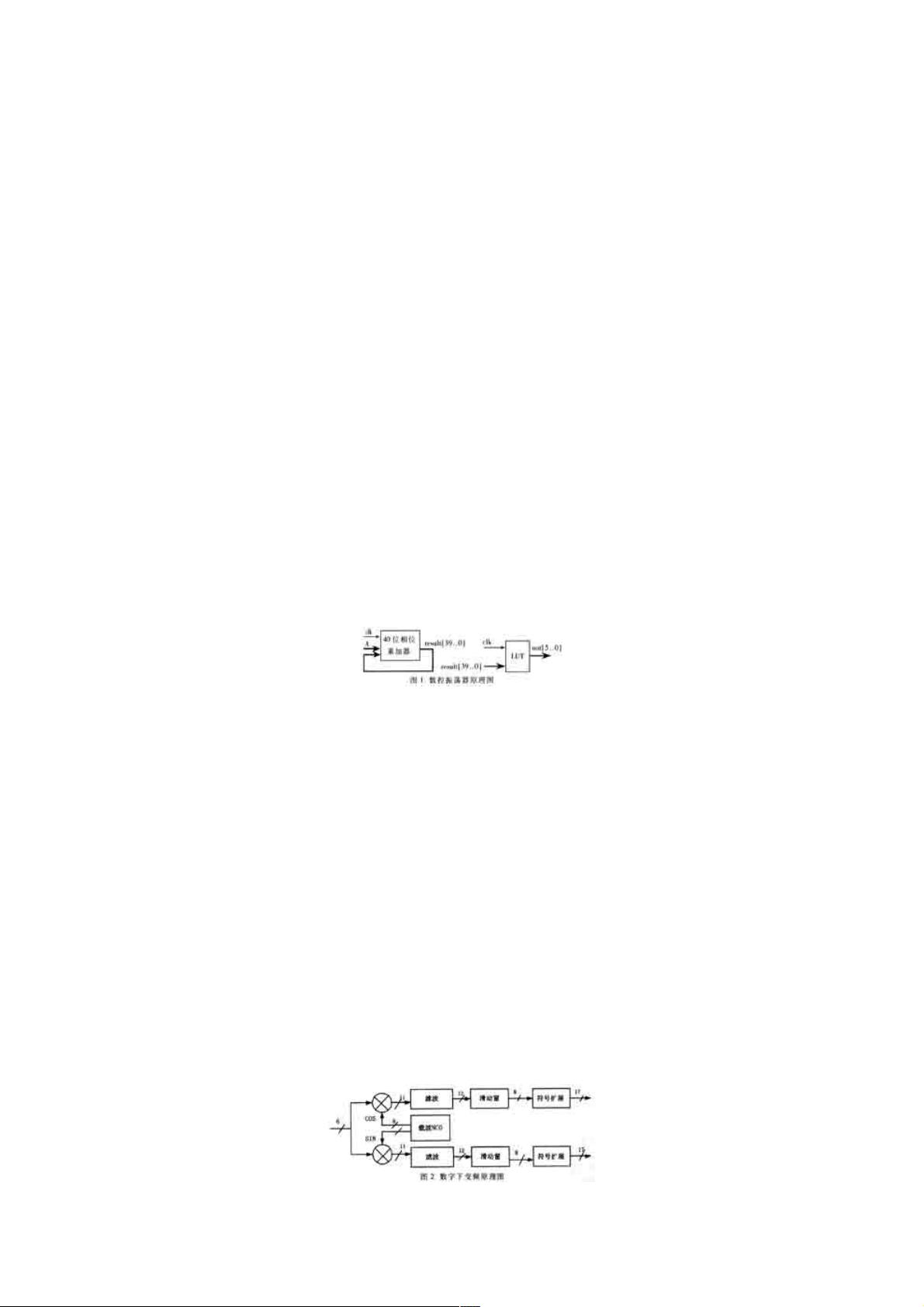

1. 数控振荡器(NCO):NCO为码发生器提供精确的时钟信号,确保对接收信号的准确捕获和跟踪。其工作原理是通过相位累加器和查找表生成所需频率。频率控制字A可以调整输出频率 fout,根据系统时钟fclk和累加器数据宽度(如40位),计算出 fout 和 Δf,以实现精细频率控制。

2. 码发生器:码发生器通常由相位累加器和查找表构成,根据NCO提供的时钟信号生成所需的伪随机码序列,用于与接收信号进行相关解扩。

3. 相关累加器:相关累加器执行相关运算,将接收到的信号与本地码序列比较,积累相同码元的匹配程度,从而判断信号的存在并估计其相位。

4. 数字下变频器:它将接收到的高频信号转换为较低的中频信号,便于后续的数字处理。

5. 伪码移相电路:调整伪码序列的相位,以适应信号可能存在的相位偏移,保证解扩的准确性。

通过FPGA实现这些功能,可以灵活地调整设计,快速响应系统需求的变化,同时减小了物理尺寸,使得混合扩频接收机更易于集成到小型设备中。此外,FPGA的并行处理能力使得整个解扩和同步过程的实时性能得以保障,提升了系统整体性能。

DS/FH混合扩频接收机的解扩及同步技术通过FPGA实现,不仅提高了系统集成度,还降低了设计复杂性,是现代通信系统小型化和高效化的有效手段。FPGA的设计灵活性和强大的逻辑综合能力为实现复杂的通信算法提供了有力支持。

2021-01-19 上传

2020-12-08 上传

2020-12-10 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38621638

- 粉丝: 1

- 资源: 983

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍