QuartusII VerilogHDL编程与仿真教程

需积分: 0 188 浏览量

更新于2024-08-05

收藏 1.03MB PDF 举报

"QuartusII使用指南,主要讲解如何使用该软件进行FPGA芯片的Verilog HDL程序设计、编译、仿真和下载。内容包括创建工程、编写Verilog HDL代码、编译工程、功能仿真以及编程下载到KX2C5F(Altera EP2C5+EPCS1)芯片。"

Quartus II是Altera公司推出的一款强大的FPGA设计软件,用于实现基于Verilog HDL或 VHDL的设计流程。在Quartus II中,设计流程通常包括以下几个关键步骤:

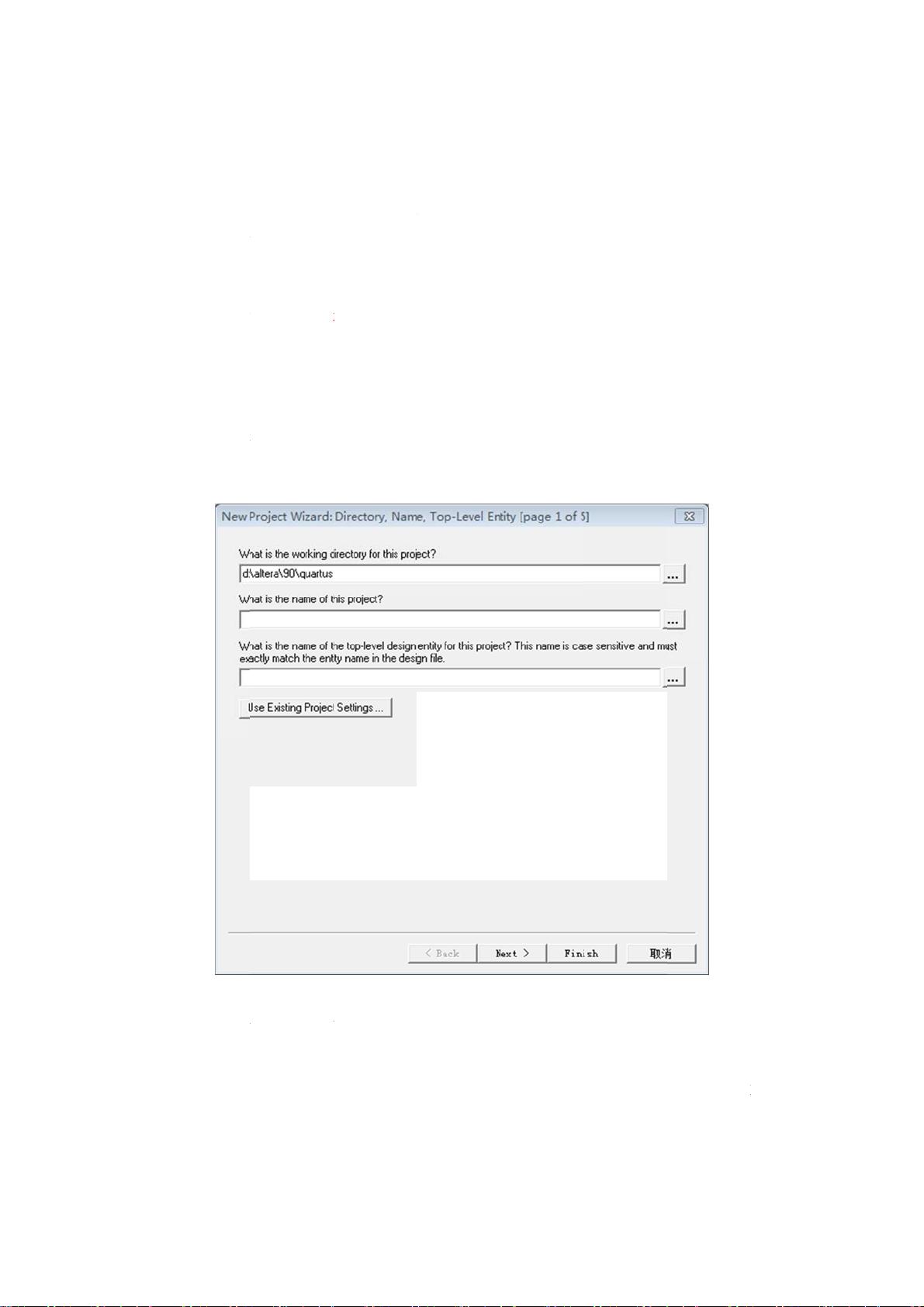

(1)创建工程:首先,打开Quartus II软件,点击“File”菜单,然后选择“New Project Wizard”。在弹出的对话框中,设定工程的存储路径、工程名,以及FPGA芯片型号(例如:Altera EP2C5+EPCS1)。

(2)新建Verilog HDL文件:在工程中,通过菜单栏“File>New”选择“Design Files”下的“Verilog HDL File”,进入Verilog HDL程序的录入编辑界面。在这里,你可以编写逻辑电路的描述代码。

(3)录入源程序:根据设计需求,使用Verilog HDL语言编写逻辑电路的描述。例如,可以创建一个4位的计数器,连接到实验开发板上的拨码开关和按键。

(4)编译:在完成代码编写后,点击“Processing>Start Compilation”进行编译。编译过程中,软件会检查语法错误和逻辑问题,并生成优化后的硬件描述。

(5)功能仿真:如果编译成功,可以进行功能仿真验证。通过“Processing>Start Simulation Tool”选择“Functiona Simulation”模式,生成仿真网表并设置仿真参数。在仿真过程中,可以观察信号的变化,验证设计的正确性。

(6)波形显示:在功能仿真后,可以通过打开波形视图,插入要观察的信号节点,如“Insert>Insert Node or Bus”,来查看仿真结果的波形图,便于分析和调试。

(7)编程下载:当设计经过验证无误后,通过“Processing>Generate Programming File”生成编程文件,然后使用合适的编程设备(如EPCS1)将设计下载到FPGA芯片上,实现硬件实现。

总结来说,Quartus II提供了完整的FPGA设计环境,从源代码编写到硬件实现,涵盖了设计、验证和下载的全过程。这个过程对于理解和掌握FPGA设计是非常重要的。通过实践和学习Quartus II,开发者可以更高效地实现复杂数字系统的硬件设计。

2021-09-29 上传

2013-05-07 上传

2022-09-19 上传

2022-09-24 上传

2021-10-04 上传

2022-09-24 上传

2021-09-30 上传

2022-09-20 上传

2022-09-20 上传

透明流动虚无

- 粉丝: 39

- 资源: 306

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全