Cisco SUP-720-MSFC3 主控板原理图解析

需积分: 12 105 浏览量

更新于2024-07-24

收藏 570KB PDF 举报

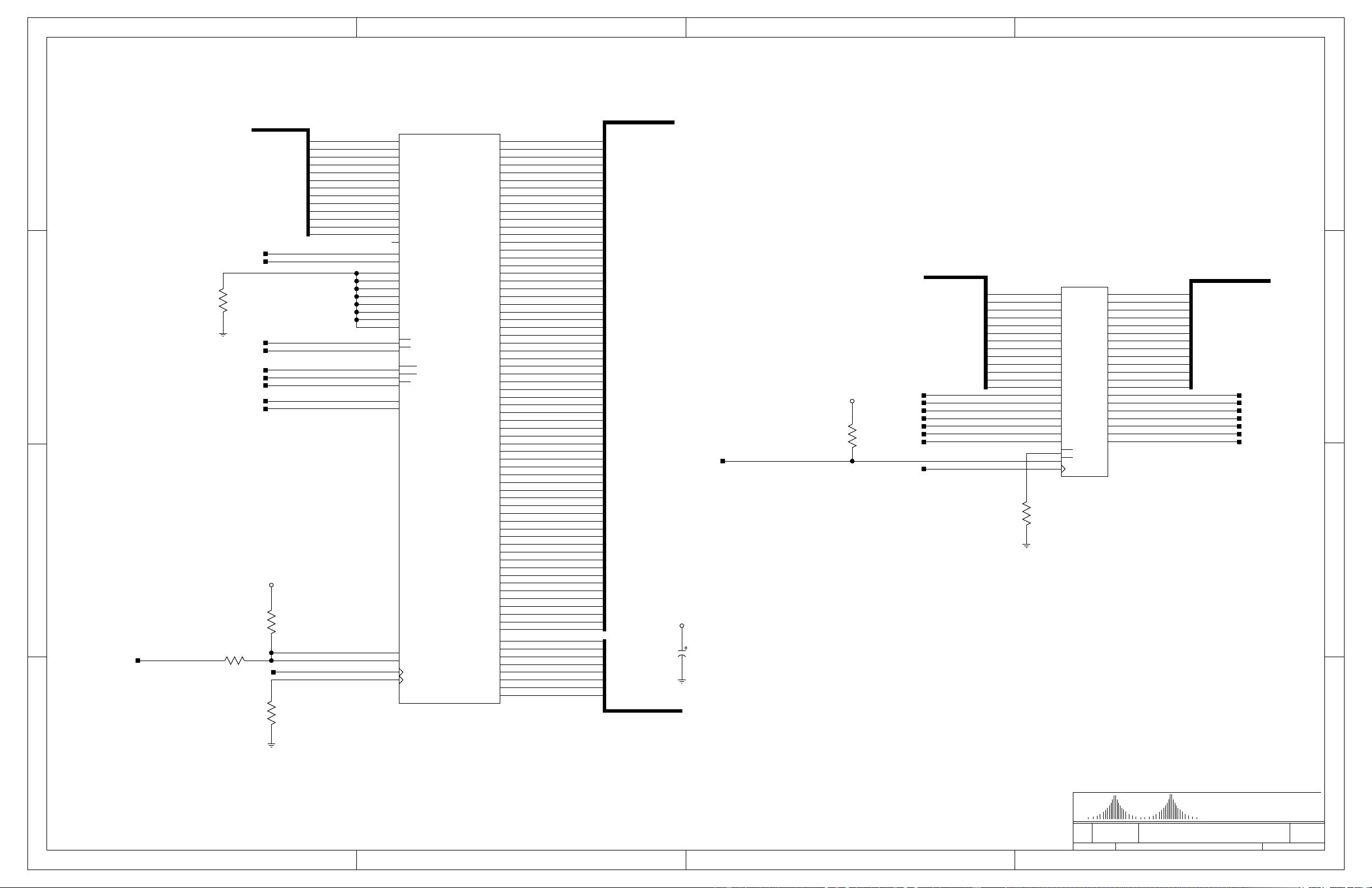

"此资源提供了Cisco产品中SUP-720-MSFC3主控板的原理图,供需要参考的人员下载。原理图涉及到的关键组件包括SANDCRAFT CPU、MISTRAL-CPU & SDRAM接口、系统SDRAM模块、MISTRAL-I/O总线、系统启动ROM、NVRAM及引导闪存、JTAG链路、以及各种电源和时钟发生器等。此外,还有I/O地址/数据锁存器和缓冲器、解耦电容、系统管理员检测器、PLL时钟发生器、CPU区域、缓存和电源调节器等模块。"

Cisco的SUP-720-MSFC3是高级路由器或交换机中的关键部件,它扮演着核心处理器的角色,负责处理网络流量和执行操作系统。原理图的详细内容揭示了其内部结构和工作原理:

1. **SANDCRAFT CPU**:这是主控板的核心,负责处理计算任务。SANDCRAFT CPU可能是一个高性能的微处理器,用于执行网络协议和服务。

2. **MISTRAL-CPU & SDRAM Interface**:这部分设计用于连接CPU与系统SDRAM,确保高效的数据传输和处理。SDRAM是系统的主要内存,提供快速访问的临时存储空间。

3. **System SDRAM Module**:存储器模块,提供大量高速数据存储,以支持CPU的运行。

4. **MISTRAL-I/O Bus**:这是主板上的输入/输出总线,允许CPU与其他组件如外部设备进行通信。

5. **System Boot ROM, NVRAM & Boot Flash**:这些组件包含启动固件,非易失性存储器(NVRAM)存储配置信息,Boot Flash则保存操作系统镜像。

6. **JTAG Chain**:联合测试行动小组(JTAG)链路,用于硬件调试和固件更新。

7. **I/O Address/Datalatches & Buffers**:这些组件确保I/O数据的稳定传输,同时处理地址和数据信号。

8. **Decoupling Caps**:解耦电容用于滤波和稳定电源,减少噪声和干扰,确保系统稳定运行。

9. **CPU Sections (CPU0 and CPU1)**:可能表示双处理器配置,提供更高的处理能力。

10. **PLL Clock Generators**:时钟发生器产生精确的时钟信号,对于同步系统操作至关重要。

11. **Baseboard Interface Connectors**:这些接口用于连接主板到其他硬件组件,如背板、电源和扩展模块。

12. **CompactFlash Connector, L3 Cache (SSRAMs & TAG), CompactFlash & Microdrive Buffers**:这些部分涉及外部存储解决方案,如CompactFlash卡,L3缓存提高性能,而缓冲器则优化数据读写速度。

13. **CPU Core Voltage Power Regulators**:为CPU核心供电的稳压器,确保恒定电压以防止过热和性能下降。

14. **SP CPU Addr Decoder & SPROM, RPCPU Addr Decoder**:地址解码器负责将CPU的总线地址转换为具体内存或I/O设备的物理地址,SPROM可能存储特定于平台的程序。

通过这个原理图,工程师可以理解和诊断硬件问题,进行故障排除,或者进行定制化修改以适应特定需求。对于维护、升级和优化Cisco设备的IT专业人员来说,这是一个宝贵的参考资料。

2012-08-03 上传

2011-09-03 上传

2011-09-15 上传

2021-06-14 上传

205 浏览量

ciscoharbour

- 粉丝: 0

- 资源: 3

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全