74HC76双J-K触发器:高速CMOS技术与电路详解

版权申诉

PDF格式 | 136KB |

更新于2024-08-02

| 94 浏览量 | 举报

"74HC76.pdf"

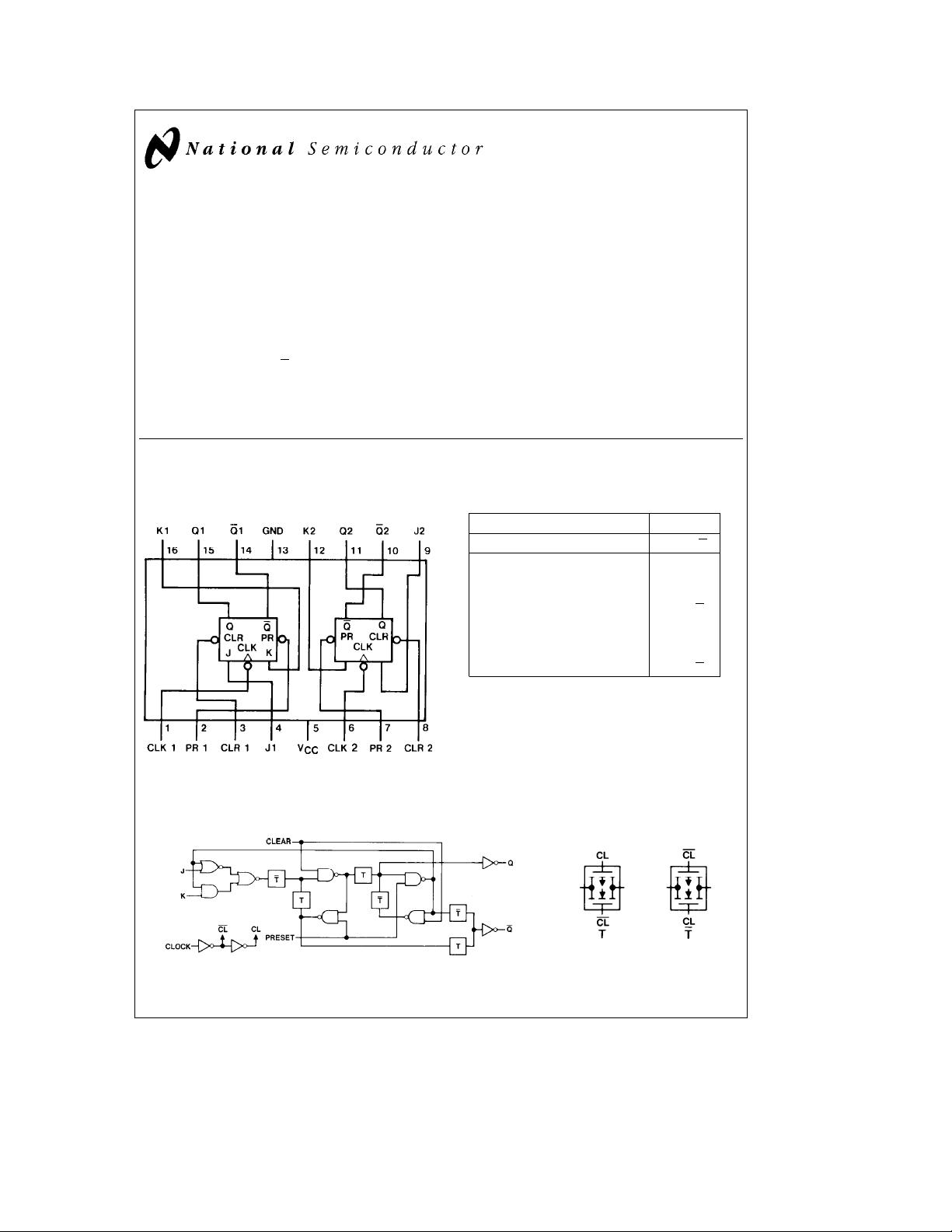

这篇文档是关于74HC76集成电路的详细资料,该芯片在电子设计竞赛中可能被用作参考,适用于大学生进行项目开发或研究。74HC76是一款双J-K触发器,带有预置(Preset)和清除(Clear)功能,常用于数字电路设计,特别是时序逻辑电路。

一、74HC76芯片特性

1. **高速性能**:这款J-K触发器具有30MHz的最小工作频率,意味着它能在高速的信号处理应用中表现出色。

2. **低功耗与高噪声免疫力**:采用先进的硅栅极CMOS(互补金属氧化物半导体)技术,降低了功耗,并增强了对噪声的抵抗能力,这使得它适合在标准CMOS集成电路中使用。

3. **独立输入与输出**:每个触发器都有独立的J、K、PRESET、CLEAR和CLOCK输入,以及Q和Q'输出。这意味着用户可以独立控制这些输入,以实现不同的逻辑功能。

4. **边沿触发**:触发器对时钟输入是边沿敏感的,状态会在时钟脉冲的负边沿转换时改变。

5. **预置与清除操作**:预置和清除操作不依赖于时钟,当对应的输入端口接收到低电平逻辑信号时立即生效。

6. **兼容性**:74HC76与标准的54LS/74LS逻辑家族在功能上和引脚布局上都兼容,方便在现有设计中替换或扩展。

7. **保护措施**:所有输入端口都有内部二极管钳位到VCC和地,以防止静电放电造成的损坏。

8. **性能指标**:典型的传播延迟为16ns,表明其快速的响应速度;工作电压范围宽,适应多种电源条件;输入电流低至1mA最大值,静态电流40mA最大(对于74HCS系列);高输出驱动能力,能驱动10个LS-TTL负载。

二、74HC76的应用场景

74HC76芯片广泛应用于需要存储和转换数字信息的系统中,如计数器、寄存器、移位寄存器等。由于其高速性能和低功耗,它在数字信号处理、计算机硬件、通信设备以及嵌入式系统设计中都有重要应用。此外,预置和清除功能使得它可以轻松地初始化或清零,增加了设计的灵活性。

三、设计注意事项

在使用74HC76时,需要考虑以下几点:

1. **电源管理**:确保电源电压在芯片的工作范围内,以保证正常工作。

2. **时序匹配**:由于触发器是边沿触发,因此在设计时需要考虑时钟和其他信号之间的时序关系,避免毛刺和竞争冒险。

3. **信号电平**:确保输入信号满足74HC76的逻辑电平要求,避免逻辑混乱。

4. **抗干扰设计**:考虑到高噪声免疫力,但仍需注意电路板上的电磁兼容性设计,避免外部噪声影响电路的稳定运行。

5. **热设计**:尽管功耗较低,但在大负载或高温环境下,仍需要考虑散热问题。

总结来说,74HC76是一款高性能、低功耗的J-K触发器,具备丰富的功能和良好的兼容性,是数字逻辑电路设计中的重要组件。理解其特性和应用原理,有助于在实际项目中有效地使用它。

相关推荐

阿拉伯梳子

- 粉丝: 2886

最新资源

- 探索99乘法表的Java源码与x86-64汇编简介

- C#实现类似QQ效果的OutlookBar源码分享

- BMP180气压高度计驱动代码在AVR单片机上的应用与优化

- 利用js原生技术实现表格行拖拽排序功能

- VB环境下的仿QQ折叠面板多行列表控件实现

- DOJO+FLEA企业门户网站开发与部署教程

- VB课程设计实战:多功能计算器源代码解析

- Java版Mochadoom源码分叉,完整Doom源端口重现

- Java实例系列之实例8:深入访问控制

- ArcGIS Web AppBuilder 2.4 开发者版本概述

- VB源码分享:一键界面换肤模块简易操作指南

- 计算机考研数据结构1800题及答案解析

- ryandashboard: 基于Angular的在线离线任务仪表板

- 设计背景的工具栏使用教程及资源下载

- 掌握阿莱多用户等级登录系统2005版的管理与权限

- 51单片机实现温湿度调节系统的C语言编程与设计