64位子字并行加法器设计:模块构建与算法实现

需积分: 10 162 浏览量

更新于2024-07-29

1

收藏 270KB DOC 举报

本篇报告详细探讨了64位子字并行加法器的设计,其核心目标是通过并行化处理提高运算性能,适用于多种数据宽度的加法,包括字节(8bit)、半字(16bit)、字(32bit)和双字(64bit)。加法器设计分为三个主要阶段:

1. 原理与系统设计:

- 报告首先阐述了64位数据的子字概念,通过划分成8个字节、4个半字、2个字或1个双字的子字进行并行运算,以提升运算效率。

- 加法器采用最小4位加法器作为底层模块,采用超前进位法,每个模块有进位输入和输出。这种结构允许通过串联进位方式构建8位基础单元加法器,最终组合成整个64位系统。

2. 模块设计:

- 4位加法器模块:作为基础单元,它接收输入变量a和b的4位二进制数据,以及进位输入ci4,输出结果s同样为4位。

- 8位加法器模块:由两个4位加法器模块串联构成,能够处理更大规模的运算,并通过控制进位传递实现不同子字模式下的加法。

3. 系统集成:

- 当输入被加数、加数以及mode(选择子字模式)和进位输入信号后,系统根据mode和进位信号智能地控制进位流程,确保正确的子字加法运算。

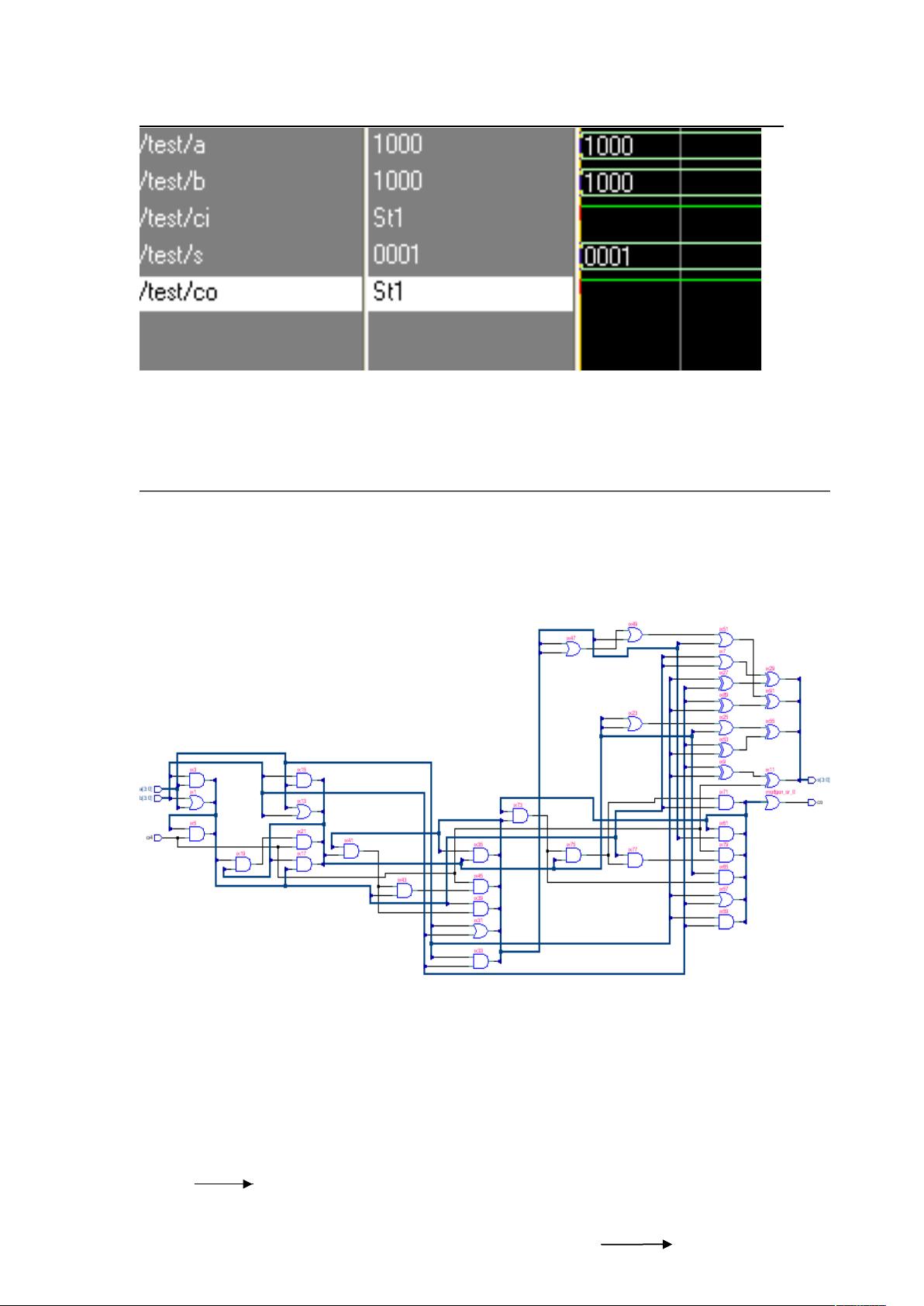

4. 电路图与测试:

- 综合后的整体电路图展示了各个模块如何连接,形成一个完整的64位加法器系统。

- 结论部分总结了设计的关键点和可能的应用场景,同时分享了设计过程中的心得体会和改进建议。

5. 其他内容:

- 报告还包含了参考文献,供读者进一步查阅;源代码和注释提供了实现这一设计的具体实现细节。

通过以上设计,作者不仅实现了高效的64位子字并行加法器,而且展示了在实际电路设计中灵活运用基础模块和进位控制策略的能力,这对于理解和实践IC课程设计具有重要价值。

2430 浏览量

381 浏览量

170 浏览量

381 浏览量

310 浏览量

2021-02-18 上传

2021-01-21 上传

点击了解资源详情

宫柯郎

- 粉丝: 20

- 资源: 13

最新资源

- Principles of Object-Oriented Programming.pdf

- 电脑完全优化手册(PDF)

- Protel DXP

- lingo教程(word文档).DOC

- C++ 面试题1.pdf

- PIC单片机C语言学习教程

- iccavr_软件中文说明书

- adc0831使用说明

- 硬盘绝密资料.pdf

- 基于单片机USB接口的数据采集存储电路的设计

- 关于MFC入门说明,挺不错的!

- 2008上半年软件设计师上午试题

- C/C++语言经典程序设计编程精解.doc

- DOS 概述及入门1

- Programming Windows Workflow Foundation

- 维互动SEO教程《搜索引擎优化魔法书》