VHDL实现:异步串行通信电路设计与波特率发生器

32 浏览量

更新于2024-09-03

收藏 121KB PDF 举报

"该文介绍了基于VHDL的异步串行通信电路设计,讨论了串行异步通信的帧格式和波特率,并详细阐述了串行发送电路的设计,包括波特率发生器的构建。"

在电子技术领域,现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)的应用越来越广泛,它们为电子系统设计提供了极大的灵活性和高效性。在这样的背景下,基于VHDL设计异步串行通信电路成为了实现高效通信的一种重要手段。

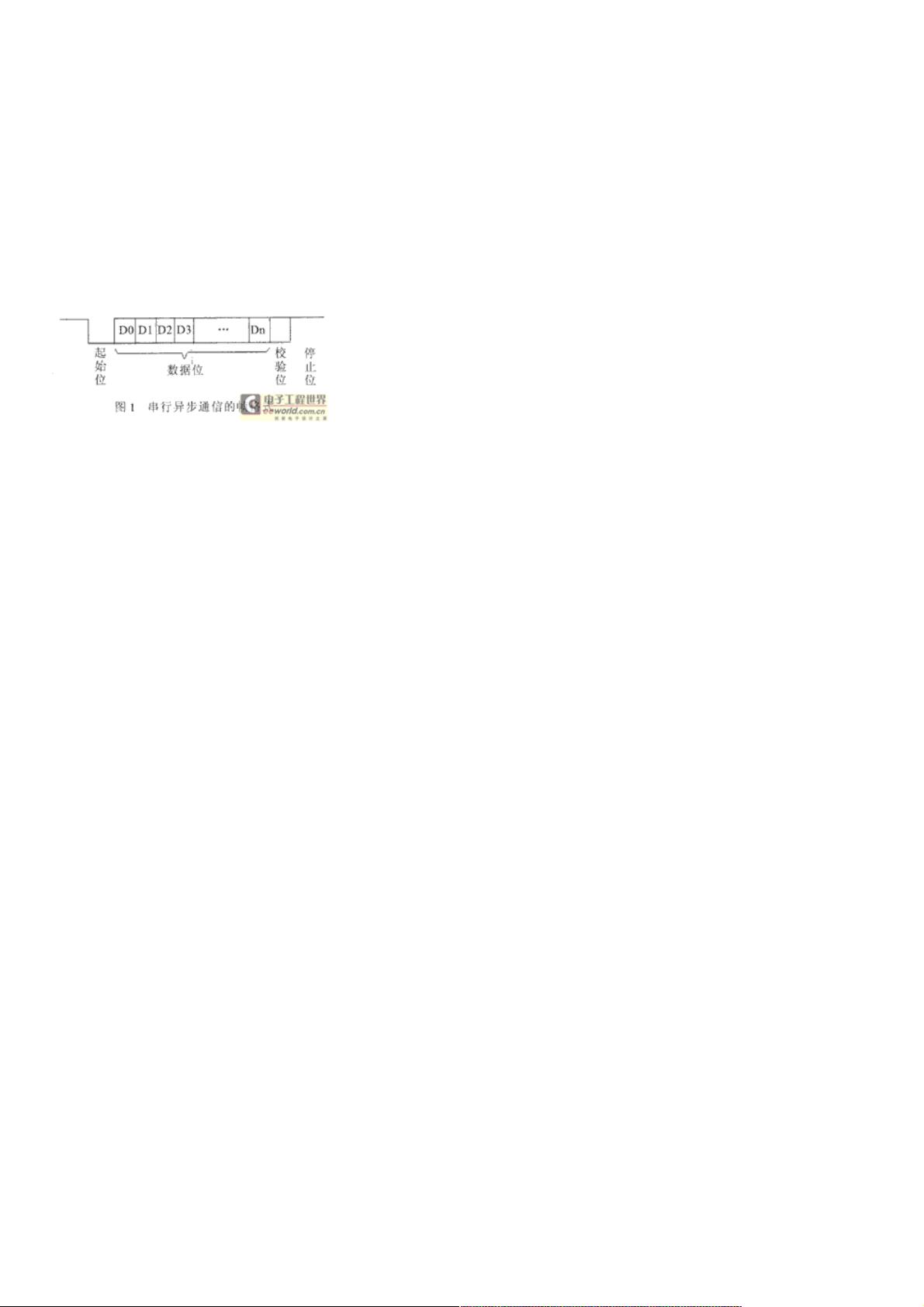

异步串行通信是一种广泛应用的数据传输方式,它的特点是数据传输速率可以与接收端不同步。在这一通信模式下,数据帧由起始位、数据位、可选的校验位和停止位组成。起始位通常为逻辑0,标志着数据传输的开始;数据位则包含实际传输的信息,根据协议可选择5、6、7或8位;校验位用于检测传输错误,可以是奇校验、偶校验,甚至是0校验或1校验;停止位是逻辑1,用于标识数据帧的结束,其长度可以是1位、1.5位或2位,目的是确保接收端有足够的时间准备接收下一个数据帧。

波特率是衡量串行通信速度的关键参数,表示每秒传输的位数。若要发送或接收一位数据需要时间t,那么波特率就是1/t,相应的时钟频率为1/tHz。在通信中,发送和接收设备的波特率必须匹配,否则会导致数据错误。

在具体设计串行发送电路时,本文选取了一种简化帧格式:1位起始位、8位数据位和1位停止位,不包含校验位,波特率为9600。为了生成这个波特率,需要一个至少为9600Hz的时钟源。在这里,作者选择了6MHz的晶振作为外部时钟,然后通过设计一个625进制的分频器来产生9600Hz的时钟信号,以满足9600波特率的要求。

VHDL是一种硬件描述语言,它允许工程师以类似于编写软件的方式描述硬件逻辑,从而简化FPGA和CPLD的开发过程。在VHDL中,波特率发生器可以通过计数器和逻辑门电路实现,计数器在每个时钟周期内递增,当达到一定阈值时复位,这样就能得到所需波特率的时钟信号。

基于VHDL的异步串行通信电路设计涉及了对通信协议的理解、时钟频率的计算和分频器的设计,这些是实现可靠、高效串行通信的基础。通过这种方式,我们可以构建出能够适应各种应用场景的自定义通信模块,满足不同系统的需求。

2023-06-22 上传

点击了解资源详情

点击了解资源详情

2010-07-15 上传

点击了解资源详情

2023-04-13 上传

2022-09-20 上传

点击了解资源详情

2021-09-17 上传

weixin_38746018

- 粉丝: 8

- 资源: 942

最新资源

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 4种常用进制转换器,2.8.10.16进制互转

- 16进制和字符串互转工具

- 二进制文件格式分析工具

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 华为简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 华三无线系统AP胖转瘦fit文件包大全

- java小白到高级之java三大集合的使用

- WPF多值转换器demo

- Java集合框架的基本接口.zip

- 简易评分系统 C++代码(EasyX)

- STM32HAL库+SPI+DMA驱动SW2812

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- python入门视频-运算符

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习